Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

опислни1

ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик фф (61) Дополнительное к авт. свид-ву— (51) Л!,Кл з 6 06 F 1/02 (22) Заявлено 19.12.72 (21) 1859990/18-24 с присоединением заявки— (23) Приоритет— (43) Опубликовано 05.03.76. Бюллетень № 9 (45) Дата опубликования описания 17.07.76

Государственный комитет

Совета Министров СССР по делам изобретений (53) УД К 681.325.5 (088.8) и открытий (72) Автор изоб,ретения

В. И. Иванов

Челябинский политехнический институт имени Ленинского Комсомола (71) Заявитель (54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области вычислительной техники и может найти применение при построении быстродействующих вычислительных устройств различного назначения.

Известны цифровые функциональные преобразователи, содержащие шифратор,,вход которого через дешифратор подключен к входу преобразователя. Цифровые функциональные преобразователи, выполненные по схеме дешифратор-шифратор имеют предельно достижимое быстродействие в один такт.

Однако они содержат большое число логических элементов, которое растет пропорционально 2", где и — число разрядов преобразователя, с увеличением точности воспроизведения функции.

Цель изобретения — сокращение оборудования преобразователя.

Это достигается тем, что преобразователь содержит блок суммирования по модулю два, выход которого подключен к выходу преобразователя, сдвигатель кодов, информационный и управляющий входы которого подключены соответственно к,входу преобразователя и выходу дешифратора и блок коррекции, вход которого соединен со входом преобразователя, выходы шифратора, сдвигателя кодов и блока коррекции подключены к соответспвующи м,входам блошка суммиравания по модулю два. Это уменьшает количество логических элементов в схеме однотактного цифрового функционального преобразователя, и, как следствие, уменьшает его стоимость, повышает надежность.

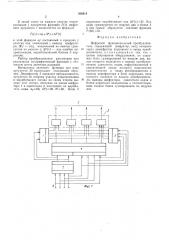

5 На фиг. 1 представлена схема цифрового функциональ:- ого преобразователя. Она содержит шифратор 1, дешифратор 2, блок 8 суммирования, одвигатель кодов 4, блок 5 коррекции, вход б и выход 7 преобразователя.

На фиг. 2 изображена логарифмическая функция F(i) цифрового аргумента 1 и способ ее аппроксимации на каждом участке. Для упрощения чертежа двоичные цифры представлены восьмеричными -ê:âèâàëåíò,àìè. На фиг. 3 изображена конкретная схема преобразователя для этого случая.

Дешифратор 2 выполняет роль выявителя участков аппроксимации функции, шифратор

1 вырабатывает код, постоянный в пределах данного участка аппроксимации, сдвигатель кодов 4 на каждом участке сдвигает код аргумента влево или вправо и тем самым умножает его на целую степень двойки. Коды шифратора;и сдвигателя суммируются в блоке 8, поскольку сложение не а рифметическое необходимая коррекция достигается прибавлением кода оши бки аппроксимации, который вырабатывается комбинационным блоком б коррекции.

506014

В такой схеме на каждом участке аппроксимации / дискретная:функция F(i) цифрового аргумента i вычисляется по формуле

Fi (i) = а/+ 2 / + ЛЕ (/) в этой формуле а/ постоянный в:пределах / участка код, снимаемый с:выхода шифратора; 2"/ — код, получаемый на выходе сдвигателя на участке j; ЛЕД вЂ” код ошибок аппроксимации, вырабатываемой блоком 5 коррекциями.

Работу преобразователя рассмотрим при реализации логарифмической функции с точностью шесть двоичных разрядов. ,Вычисление значения функции .при,коде аргумента 30 происходит следующим образом. Дешифратор 2 выявляет принадлежность аргумента ко второму участку аппроксимации и вырабатывает сигнал на своем втором выходе, этот сигнал, поступая на входы шифратора 1 и сдвигателя 4, заставляет их выработать коды а2=60, i2 j 30 2 =30. Блок 5 коррекции вырабатывает код ЛР(Ц =01. Все коды суммируются по модулю два в блоке 3 и тем самым образуется значение функции

F (30) ==51.

Формула изобретения

Цифровой функциональный преобразователь, содержащий шифратор, вход которого

10 через дешифратор подключен к входу преобразователя, отл и ч а ющи и ся тем, что, с целью сокращения оборудования, он содержит блок суммирования по модулю два, выход которого подключен к выходу преобразо15 вателя, сдвигатель кодов, информационный и управляющий входы которого подключены соответственно .к входу преобразователя и выходу дешифратора и блок коррекции, вход которого соединен со входом .преобразовате20 ля, выходы шифратора, сдвигателя кодов и блока коррекции, подключены к соответствующи м входам блока суммирования по модулю два.

506014

rN

1 уны ок

2@0 ! фд ИКц и

Фаз. я

Редактор О. Филиппова

Корректор И. Симкина

Заказ 562 854 Изд. № 256 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Тнп. Харьк. фил. пред. «Патент»

Г1 Я

З Л я

J y! ÓÆ 7" gy с; =gg

Составитель А. Жеренов

Техред М. Семенов