Матричный накопитель

Иллюстрации

Показать всеРеферат

ОП ИСАЙИ Е

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик!

») 506060 (61) Дополнительное к авт, свид-ву (22) Заявлено 18.07.73 (21) 194662 1/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.03.76,Бюллетень № 9 (45) Дата опубликования описания 22.09.76. (51) М. Кл. Q 11 С 11/34

Государственный комитет

Совета Министров СССР па делам изобретений и открытий (53) УДК 681.327.66 (088. 8) (72) Авторы изобретения

B. П. Андреев и А. H. Пресняков (71) Заявитель Особое конструкторское бюро вычислительной техники Рязанского р адиотехнического института (54) МАТРИЧНЫЙ НАКОПИТЕЛЬ

Изобретение относится к области вычислительной техники и может быть использовано для построения постоянного запоминающего устройства (ПЗУ) с электрической перезаписью. 5

Известны матричные накопители, содержащие ячейки памяти, каждая из которых состоит из запоминающего элемента, выполненного на основе аморфного полупроводника, и разделительного элемента, разрядные и адресные шины, резисторы. Недостат« ком таких накопителей являются невысокие эксплуатационные характеристики (большое количество контактов), низкая надежнос ть.

1Яель изобретения - улучшить эксплуатационные хар актеристики м атричного н акопителя и повысить его надежность. Зто достигается тем, что разделительный элемент gp выполнен в виде биполярного транзистора, коллектор которого подключен к первому электроду запоминающего элемента, эмиттер через резистор — к первой адресной шине, б аз а — к второй адрес ной шине, второй электрод запоминающего элемента подключен к разрядной шине.

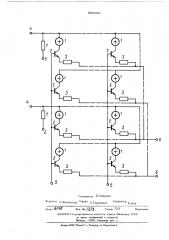

Н а чертеже пок аз ан а электрическ ая схем а предлагаемого матричного накопителя.

Матричный накопитель состоит из запоминающих элементов (ЗЭ) на основе аморфного полупроводника (в частности, халькогенидного стекла) 1, транзисторов 2, резисторов 3, разрядных шин 4, координатных шин Х 5, координатных шин У 6, резисторов 7.

Накопитель работает следующим образом.

В случае, если не происходит обращения к запоминающему устройству, на координатные шины Х подается нулевой потенциал, а на шины У вЂ” положительный. При этом все транзисторы 2 закрыты, так как напряжение эмиттер-база больше нуля.

При выборе числа на соответствующую шину Х подается положительный потенциал, а на соответствующую шину У - нулевой.

В данном случае транзисторы выбранного слова открыты, что позволяет протекать току через ЗЗ выбранных ячеек памяти.

Транзисторы, которые подключены к вы506060

3 бранной шине Х и к невыбранным шинам У, и транзисторы, которые подключены к выбранной шине У и к выбр анным шинам Х, закрыты, так как напряжение эмиттер-база равно нулю, Остальные транзисторы закры- Э ты, так как напряжение эмиттер-база больше нуля.

При работе с ЗЭ на основе аморфных полупроводников различают три режима: стирание, запись и считывание. Эти три ре-10 жим а отличаются длительностью импульсов тока через ЗЭ и их амплитудой. Обнуление ячеек памяти осуществляется в режиме стирания.

В предлагаемом накопителе этот режим осуществляется следующим образом. Выбирается число, на разрядные выводы подается импульс напряжения длительностью, соответствующей режиму стирания, на выбранную шину Х (и на невыбранные шкны У) подается напряжение, величина которого задает ток стирания. Разделительный элемент является здесь генератором тока для

ЗЭ выбранной ячейки памяти.

В режиме записи величина напряжения, подаваемого на выбранную шину Х (и на невыбранные шины У ), задает ток записи.

На разрядные шины 4 подается напряжение, необходимое для записи в том случае, если в данном разряде записывается "1". Дли30 тельность этого импульса напряжения соответствует режиму записи. При записи "0" напряжение на разрядный вывод не подает» ся и ток через ЗЭ ячейки памяти не течет.

При считывании амплитудой напряжения, подаваемого на выбранную шину Х (и невыбранную шину У), задается такая амплитуда тока через ЗЭ ячейки памяти, на4 ходящейся в состоянии "1", чтобы разделительный транзистор был близок к режиму насыщения. B этом случае напряжение на разрядной шине 4 (в режиме считывания разрядные шины являются выходом матрицы) значительно отличается от напряжения Е за счет протекания тока считывания через резистор 7. Если ячейка памяти хранит "0" (высокоомное состояние

ЗЭ), то разделительный транзистор находится в облжти насыщения и, в связи со значительным отношением сопротивления

ЗЭ в Bb?coKoolvJHDM состоянии к сопротивлению ЗЭ в низкоомном состоянии, ток через резистор 7 значительно меньше, чем ток при считывании "1", а выходное напряжение близко к Е.

Формула изобретения

Матричный накопитель, содержащий ячейки памяти, каждая из которых состоит из запоминающего элемента, выполненного на основе аморфного полупроводника, и разделительного элемента, разрядные и адресные шины, резисторы, о т л и ч а юшийся тем, что, с целью улучшения эксплуатационных характеристик и повышения надежности накопителя, в нем разделительныи элемент выполнен в виде биполяр ного транзистора, коллектор которого подключен к первому электроду запоминакнцего элемента, эмиттер через резистор - к первой адресной шине, база — к второй адресной шине, второй электрод запоминающего элемента подключен к разрядной шине.

Составитель В АндРеев

Редактор О.филиппова Техред З т ароненко

Корректор

Н.А ук

Заказ бУ В Изд. hb /3/3 Тираж 72- 1 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4