Двоично-десятичный счетчик

Иллюстрации

Показать всеРеферат

\;,„.

i=A н и

Р11 506I3l

СПИ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.04.74 (21) 2016392/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 05.03.76. Бюллетень № 9

Дата о публикования описания 06.05.76 (51) M. Кл. Н ОЗК 23,02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.3.055:621..374.32 (088.8) (72) Авторы изобретения

В. А. Грехнев и Б. Л. Останков (71) Заявитель (54) ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК

Изобретение относится к вычислительной технике, предназначено для сложения последовательности входных импульсов в двоичнодесятичном коде.

Известен двоич но-десятичный счетчик, каждый разряд которого содержит триггер памяти, коммутационный триггер и схему

«И — НЕ», причем единичный выход триггера памяти соединен с единичным входом коммутационного триггера, нулевые выходы коммутационных триггеров первого, второго и третьего разрядов соединены с единичными входами триггера памяти своих разрядов и с нулевыми входами коммутационных триггеров, триггеров памяти и схем «И вЂ” НЕ» всех более младших разрядов, вь1ходы схем

«И†HE» первого и второго разрядов соединены со входами коммутационных триггеров второго и третьего разрядов, соответственно, единичные выходы коммутационных триггеров первого, второго и третьего разрядов соединены со входами схем «И вЂ” НЕ» своего разряда, нулевые входы коммутационных триггеров всех разрядов и вход схемы «И — НЕ» четвертого разряда соединен с нулевыми входами коммутационных триггеров, триггером памяти и схем «И вЂ” НЕ» всех разрядов, нулевой выход коммутационного триггера четвертого разряда соединен с единичным входом триггера памяти четвертого разряда и нулевыми входами коммутационных триггеров первого и второго разрядов и триггера памяти первого разряда.

Цель изобретения — уменьшение количества оборудования.

Предлагаемый счетчик отличается тем, что выход схемы «И — HE» четвертого разряда соединен со входом схемы «И — HE» первого разряда, выход, которой соединен с нулевым вхо1р дом коммутационного триггера четвертого разряда, выход схемы «И — HE» третьего разряда соединен со входом схемы «И — НЕ» четвертого разряда, единичный выход триггера памяти четвертого разряда соединен с нулевым вхо15 дом коммутационного триггера второго разряда.

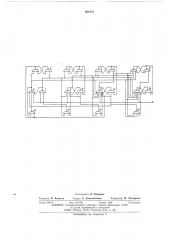

На чертеже изображена структурная схема счетчика.

Двочино-десятичный счетчик состоит из схем

«И — HE» 1 и 2, 3 и 4, 5 и 6, 7 и 8, образующих триггеры памяти, схем «И вЂ” НЕ» 9 и 10, 11 и

12, 13 и 14, 15 и 16, образующих коммутационные триггеры соответственно четвертого, третьего, второго и первого разрядов счетчика, а также схем «И вЂ” НЕ» 17 — 20.

В исходном состоянии триггеры памяти всех разрядов находятся в состоянии «нуль». Поскольку тактирующий сигнал отсутствует и на выходах схем «И вЂ” HE» 4 — 6 — логический

3р нуль, то на выходах схем «И вЂ” HE» 11 — 17—

506131 логическая единица. Следовательно, па выходах схем «И- НЕ» 10, 18- — 20 — логический нуль. Таким образом, с приходом первого тактирующего импульса срабатывает только схема «И вЂ” HE» 15, устанавливая триггер памяти первого разряда в состояние «единица». По окончании действия тактирующего сигнала на выходе схемы «И — HE» 20 появляется сигнал, равный логической единице. Следовательно, с приходом следующего тактирующего сигнала срабатывает схема «И вЂ” НЕ» 13, устанавливая триггер памяти второго разряда в состояние

«единица», а триггер памяти первого разряда — в состояние «нуль».

Чтобы схема «И вЂ” НЕ» 15 первого разряда не могла сработать в момент действия этого тактирующего сигнала после того как триггер памяти первого разряда установится в состояние «нуль», а также для обеспечения устойчивой работы схемы «И — HE» 13, выход этой схемы «И — HE» соединен со входами схем

«И — HE» 15 и 20. Таким образом, сигнал на выходе схемы «И — HE» может измениться лишь по окончании действия тактирующего сигнала. С приходом третьего тактирующего сигнала срабатывает только схема «И вЂ” HE»

15, поскольку па выходах схемы «И — HE» 10, 18 — 20 — логические нули. По окончании действия тактирующего сигнала на выходе схемы «И — HE» 20 оказывается логическая единица, а поскольку триггер памяти второго разряда находится в состоянии «единица», на выходе схемы «И — HE» 19 — также логическая единица. Таким образом, с приходом четвертого тактирующего импульса схема «И вЂ” HE» 11 устанавливает триггер памяти третьего разряда в состояние «единица», а триггеры памяти второго и первого разрядов — в состояние

«нуль». Наличие связи с выхода схемы

«И — НЕ» 11 на входы схем «И вЂ” HE» 13, 15, 19 опять препятствует неправильной работе счетчика. Аналогичным образом с приходом восьмого тактирующего импульса схема

«И — НЕ» 17 устанавливает триггер памяти четвертого разряда в состояние «единица», а триггеры памяти остальных разрядов — в состояние «пуль». С приходом девятого тактирующего импульса срабатывает схема «И вЂ” НЕ»

15, и в счетчике устанавливается код 1001.

С приходом десятого тактирующего сигнала схема «И вЂ” HE» 13 не срабатывает, поскольку на выходе схемы «И — HE» 1 — логический г

25 зв

50 нуль. Поэтому срабатывает только схема

«И — НЕ» 9, которая устанаьливает триггеры памяти четвертого и первого разрядов в состояние «нуль». Наличие связи с выхода схемы

«И — HE» 9 на входы схем «И вЂ” HE» 10, 13, 15 и 20 опять препятствует неправильной работе счетчика, Таким образом, схема возвращается в исходное состояние, в счетчике устанавливается код 0000, и цикл работы счетчика повторяется.

Формула изобретения

Двоично-десятичный счетчик, каждый разряд которого содержит триггер памяти, коммутационный триггер и схему «И — НЕ», причем единичный выход триггера памяти соединен с единичным входом коммутационного триггера, нулевые выходы коммутационных триггеров первого, второго и третьего разрядов соединены с единичными входами триггеров памяти своих разрядов и с нулевыми входами коммутационных триггеров, триггеров памяти и схем «И вЂ” НЕ» всех более младших разрядов, выходы схем «И вЂ” HE» первого и второго разрядов соединены со входами коммутационных триггеров второго и третьего разрядов соответственно, единичные выходы коммутационных триггеров первого, второго и третьего разрядов соединены со входами схем «И вЂ” НЕ» своего разряда, нулевые входы коммутационных триггеров всех разрядов и вход схемы

«И — НЕ» четвертого разряда соединены со входом счетчика, выход схемы «И — HE» четвертого разряда соединен с нулевыми входами коммутационных триггеров, триггеров памяти и схем «И вЂ” НЕ» всех разрядов, нулевой выход коммутационного триггера четвертого разряда соединен с единичным входом триггера памяти четвертого разряда и нулевыми входами коммутационных триггеров первого и второго разрядов и триггера памяти первого разряда, отличающийся тем, что, с целью уменьшения количества оборудования, выход схемы

«И — НЕ» четвертого разряда соединен со входом схемы «И — НЕ» первого разряда, выход которой соединен с нулевым входом коммутационного триггера четвертого разряда, выход схемы «И — НЕ» третьего разряда соединен со входом схемы «И — HE» четвертого разряда, единичный выход триггера памяти четвертого разряда соединен с нулевым входом коммутационного триггера второго разряда.

Редактор Б, Федотов

Составитель В. Назарова

Техред А. Камышникова Корректор М. Лейзерман

Заказ 944/16 Изд. № 258 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., p,. 4/5

Типография, пр. Сапунова, 2