Устройство переменного приоритета

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

011 506854

Соме Советских

Социалистических

РесптИик (61) Дополнительное к авт. свид-ву (22) Заявлено 30.04.74 (21) 2021872/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.03.76. Бюллетень № 10

Дата опубликования описания 10.05.76 (51) Ч Кч е G 06F 9118

Госудлрственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УД К 681.325 (088.8) (72) Авторы изобретения Б. Н. Малиновский, С. И, Самарский, В. А. Иванов и П. М. Сиваченко (71) Заявитель Киевский ордена Трудового Красного Знамени завод электронных вычислительных и управляющих машин (54) УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА

Изобретение относится к области вычислительной техники и в частности к устройствам, обеспечивающим переменную приоритетность сигналов прерывания в электронных вычислительных машинах.

Известно устройство переменного приоритета, содержащее регистр приоритета, кодовый выход которого соединен с кодовым входом счетчика, блок управления, выходы которого соединены с управляющими входами регистра приоритета, циклического регистра сдвига и со счетным входом счетчика.

С целью сокращения оборудования устройства оно содержит блок анализа на нуль счетчика и блок анализа на единицу старшего разряда циклического регистра сдвига, входы которых соединены с выходами соответственно счетчика и циклического регистра сдвига, а выходы — с соответствующими входами блока управления.

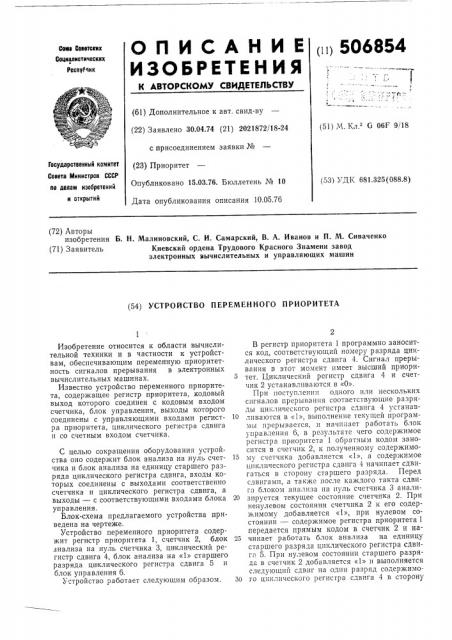

Блок-схема предлагаемого устройства приведена на чертеже.

Устройство переменного приоритета содержит регистр приоритета 1, счетчик 2, блок анализа на нуль счетчика 3, циклический регистр сдвига 4, блок анализа на «1» старшего разряда циклического регистра сдвига 5 и блок управления 6.

Устройство работает следующим образом.

В регистр приоритета 1 программно заносится код, соответствующий номеру разряда циклического регистра сдвига 4. Сигнал прерывания в этот момент имеет высший приоритет. Циклический регистр сдвига 4 и счетчик 2 устанавливаются в «О».

При поступлении одного или нескольких сигналов прерывания соответствующие разряды циклического регистра сдвига 4 устанав10 ливаются в «1», выполнение текущей программы прерывается, и начп ает работать блок управления 6, в результате чего содержимое регистра приоритета 1 обратным кодом заносится в счетчик 2, к полученному содержимому счетчика добавляется «1», а содержимое циклического регистра сдвцга 4 начинает сдвигаться в сторону старшего разряда. Перед сдвигами, а также после каждого такта сдвига блоком анализа па нуль счетчика 3 анали20 зпруется текущее состояние счетчика 2. При ненулевом состоянии счетчика 2 к его содержимому добавляется «1», при нулевом состоянии — содержимое регистра приоритета 1 передается прямым кодом в счетчик 2 и на25 чинает работать блок анализа на единицу старшего разряда циклического регистра сдвига 5. При нулевом состоянии старшего разряда в счетчик 2 добавляется «1» и выполняется следующий сдвиг на один разряд содержимо30 го циклического регистра сдвига 4 в сторону

506854

55 старшего разряда, после чего анализ о состоянии старшего разряда регистра сдвига 4 погторяется и т. д. При единичном состоянии старшего разряда блок управления 6 отключается, а содержимое счетчика 2 используется в качестве модифицируемой части адреса перехода на соответствующую программу.

Пусть, например, разрядность регистра приоритета 1 и счетчика 2 равна четырем, а разрядность циклического регистра сдвига 4— шестнадцати. В регистре приоритета 1 содержится код 0101. Поступает сигнал прерывания в третий разряд циклического регистра сдвига 4

Содержимое регистра приоритетов 1 обратным кодом передается в счетчик 2, и к содержимому счетчика 2 добавляется единица. В результате в счетчике будет код 1011.

Начинаются сдвиги содержимого циклического регистра сдвига 4 одновременно со счетом числа сдвигов в счетчике 2 (суммированием с кодом 1011) и анализом на нуль его содержимого. После выполнения пяти сдвигов в счетчике 2 будет «О», старший по приоритету разряд циклического регистра сдвига 4, определенный кодом в регистре приоритета 1, сдвинется на место старшего разряда регистра 4, а единица в третьем разряде циклического регистра сдвига 4 передвинется в четырнадцатый разряд. Так как в регистре приоритета 1 код 0101 (5), то расположение сигналов прерывания в порядке их приоритетов будет следующим: «5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, О, 1,2,3,4».

Код 0101 из регистра приоритета 1 записывается в счетчик 2, после чего сдвиги содержимого циклического регистра сдвига 4 будут продолжены со счетом числа сдвигов (суммированием с кодом 0101) и анализом на единицу старшего разряда.

Если сигналов прерывания с номерами «5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, О, 1, 2» не поступало, то в 0 — 13 разрядах циклического регистра сдвига 4 будут нули. После выполнения четырнадцати сдвигов срабатывает блок анализа на единицу старшего разряда циклического регистра сдвига 5 и отключает блок управления 6.

Код в счетчике 2 будет: 0101+ 1110= 10011.

Поскольку разрядность счетчика 2 равна четырем, старший разряд суммы теряется, а содержимое счетчика 2 соответствует номеру разряда прерывания. По этому коду формируется адрес перехода к прерывающей программе.

Код в регистре приоритета 1 определяет переменные значения приоритетов сигналов прерывания.

При программном изменении содержимого регистра 1 изменяется номер разряда циклического регистра сдвига 4, значение которого сдвигается в старший разряд регистра, начиная с которого будет осуществляться его анализ на «О» и «1». Разряды, отстоящие от анализируемого в сторону младших разрядов регистра, анализируются позже и имеют постепенно уменьшающийся приоритет.

Общее число позиций приоритета устройства и каждого прерывающего сигнала соответствует разрядности циклического регистра сдвига 4.

Быстродействие известного и рассматриваемого устройства, т. е. время реакции на сигнал прерывания, зависит как от номера разряда сигнала прерывания, так и от кода в регистре приоритета.

Если принять время одного такта сдвига и передачи между регистрами за 0,2 мксек, то задержка времени реакции в известном устройстве составляет от 0,2 до 3,2 мксек в зависимости от кода в регистре приоритета 1 и номера разряда прерывания, в рассматриваемом устройстве — соответственно от 0,4 до

6,4 мксек. При повышении рабочей частоты элементов это время будет уменьшаться. Для вычислительных систем, временные характеристики которых позволяют использовать известное устройство, указанное различие времени реакции не является существенным.

Формула изобретения

Устройство переменного приоритета, содержащее регистр приоритета, кодовый выход которого соединен с кодовым входом счетчика, блок управления, выходы которого соединены с управляющими входами регистра приоритета, циклического регистра сдвига и счетным входом счетчика, о тл и ч а ю щ ее с я тем, что, с целью сокращения оборудования, оно содержит блок анализа на нуль счетчика и блок анализа на единицу старшего разряда циклического регистра сдвига, входы которых соединены с выходами соответственно счетчика и циклического регистра сдвига, а выходы— с соответствующими входами блока управления.

506854

Заказ 947/15 Изд 1," 1172 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4)5

Типография, пр Сапунова, 2

Составитель Ф. Шагиахметов

Pедактop Г. Мозжечкова Техред T. Колесова

Корректоры: Н. Аук и И. Позняковская