Дискриминатор задержки огибающей и фазы несущей

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

Cоктз Санат.>.чх

Социалистических

Республик (l l) 507826

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву№416818 (2g) Заявлено28.05.74 (21) .2030449/26-21 с присоединением заявки (23) Приоритет(43) Опубликовано25.03.76. Бюллетень №11 (45) Дата опубликования описания 20.04.76 г (51} М. Кл.

G 01 В 23/06

Н03 а 13/OO

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) о ДК

621. 396.621,55 (088. 8) В. Н. Лукин, В. A. Кабанов и В. B. Шкирятов(72) Авторы изобретения (71) Заявитель (54) ДИСКРИМИНАТОР ЗАДЕРЖКИ ОГИБАЮШЕЙ И ФАЗЫ

НЕСУШЕЙ

Изобретение относится к радиотехнике и может быть использовано в радиолокации и радионавигации.

Известен дискриминатор задержки огибающей и фазы несущей по основному авт. св. ¹ 416818.

Однако известный дискриминатор имеет недостаточную точность измерения задержки огибающей, 11елью изобретения является увеличение точности работы усчройства.

Для этого в предлагаемый дискриминатор введены три коммутатора, фазовращатель, фильтр нижних частот и инвертор.

Выход блока опорных частот подключен к управляемым входам коммутаторов, два из которых включены между смесителями и узкополосными фильтрами, а третий подкшочен ко входу блока оценки сигнала синхронизации. При этом выход перемножителя соединен со входами третьего коммутатора, инверторв и фильтра нижних частот, выход которого соединен с управляемым

4 входом фазовращателя,, включенного между вторым коммутатором и узкополосным фильтром.

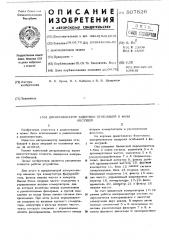

Нв чертеже представлена блок-схема дискриминатора задержки огибающей и фазы несущей, Она содержит балансный перемножитель

1,блок 2 копии сигнала, усилители 3 и 4 промежуточных частот, смесители 5 и 6, узкополосныефильтры 7 и 8 (перемножитель) фазовый детектор 9, фильтр двойной промежуточной частоты 10, фазовый компаратор 11, блок 12,<««" сигнала синхронизации, блок 13 опорных частот,, бал внсный модулятор 1 4, фильтр 1 5 ниж35 них частот, управляемый напряжением ге нератор 16, коммутаторы 17-19, фазоврвщатель 20, инвертор 21 и фильтр 22 нижних частот.

3а счет введенных коммутаторов 17-19

2О режим работы дискриминатора состоит из периодически повторяющихся с частотой коммутации двух циклов. В первом цикле выходы смесителей 5 и 6 подключены ко входам узкополосных фильтров 7 и 8, а

25 выход фазового детектора 9 непосредствен507826

Сигналы оценки с выхода балансного перемножителя 1 через усилители 3 и 4 промежуточных частот поступают на смесители 5 и 6, на входы которых одновременно подводится с выхода балансного модулятора 14 сигнал оценки л л л л

s(nf(+au-8<((ц ((>д,> -+ >ia с " О ). где 4 tQÎ м — разница опорной и промежуточной частот;

89 =+ p - ошибка оценки (1азы сигнала несущей; л

Втс=Ч> Рс — ошибка оценки фазы сигнала синхронизации;

BAgp A. -P -ошибка по частоте слежеgc "Цс ния эа допплеровским сигл и, Sin((h дg ц ba налом частоты синхрони30 л л дс н с о 9

) t- 6" P -6 (+ Р +а9+А 1(где 4+y И9 — паразитный сдвиг фазы сигнала в узкополосных фильтрах 7 и 8;

4 ро — сдвиг фазы сигнала в фазоврещателе 20. ба((24чц, - 26 Я@,1 -М9„2(„".ь, 4 Ð 4 „), фазового детектора 9 выделяется низкочастотная составляющая сигнала, пропорциональная разности фаз

50 а на выходе инвертора 23

С ) л л

4 9 = t +дС< о++С а Р +И

8 0 но ко входу блока оценки сигнала синхронизации 1 2.

Во втором цикле выходы смесителей 5 и 6 подключены соответственно ко входам узкополосных фйльтров 7 и 8, а выход фазового детектора 9 через инвертор

2 1 — ко входу блоке 12 оценки сигнала синхронизации.

Устройство работает следующим образом. который поступает на фазовый комператор

1 1. Низкочастотная составляющая выходного сигнала (перемножителя) детектоВо втором цикле текущая фаза сигнела на выходе фильтра двойной промежуточной частоты 10 не изменяется, а на выходе

Частота коммутации выбирается такой, чтобы за время каждого цикле, с одной

ЯЫ(4ю и ) t9 )йп(а „t Ч )Б(п((н и ((ич 9 )+

+ 811lt(®î с A((t) t с о1.где (N(.„ — частота синхронизации;

Я вЂ” оценка допплеровского сдвига частоты синхронизацик; P(» - оценка текущей фазы сигнала синхронизации; (k>0 — частота опорного сигнала; Ро - начальная фаза опорного сигнала.

В результате перемножения на смесителях 5 и 6 в первом цикле на выходе узкополосного фильтра 7 выделяется сигнал зации;

tQ. н=Й Й -ошибка по частоте слежения эа допплеровским сдвигом частоты несущей.

На выходе узкополосного фильтра 8 выделяется сигнал

Эти сигналы поступают на (перемножияк тель) фазовый детектор 9, на выходе которого фильтром двойной промежуточной частоты 10 выделяется сигнал вида ра 9, управляющая блоком оценки сигнала синхронизации 12, пропорциональна разности фаэ этих сигналов л

С 7 Я стороны успевали устанавливагься кол ба

@> ния в узкополосных фильтрах 7 и 8, е, с

507826 другой стороны, составляющая управляющего сигнала фазового детектора 9, соответствующая частоте коммутации, сглаживалась в блоке оценки сигнала синхронизации 12. 5

При этих условиях усредненный сигнал пропорционален: (Я) (2) л р = 1 ьФ = 289.. t 4"

Q: 12 42.

Отсюда следует, что в режиме синхрони зации, когда разность фаз стремится к нулю, оценка фазы сигнала синхронизации в блоке оценки сигнала синхронизации 12 практи ески не зависит от нормальных 15 ошибок, вызываемых неидентичностью и нестабильностью фазовых характеристик

t узкополосных фильтров 7 и 8, а также нестабильностью нуля фазового детектора 9.

Таким образом, при нахождении рабочей рО точки фазового детектора 9 в линейной (Ю (О с г - адФ, +ьФ,Е - 1 я,- Ъ - ро

2.2. и

25 отличающийся тем,что,с цепью увеличения точности работы устройства, в него введены три коммутатора, фязоврящятель, фильгр нижних частот и инвертор,. причем выход блока опорнкt частот подключен к управляемым входял коммутаторов, два из которых вк ючены между смесителями и узкополосными фильтрами, а третий подключен ко входу блока оценки сигнала синхронизации, прн этом выход перемножитепя соединен со входами третьего коммутатора, инверторя н фильтра нижних частот, выход которого

;".îåäèhåH с управляемым BxofloM фазовр»щателя, включенного между вторым коммутатором и узкополосным фильтром.

ЦНИ!;ПИ Заказ !39

Филиал ППП "Патент", r, Ужгород, ул. Гагарина, 10) Управляемый фазовращатель 20 изменяет фазовый сдвиг таким образом, чтобы (дЧ )-- О, удерживая тем самым рабочую точку фазового детектора в окрестности нулевых рассогпясований.

Таким образом, устройство позволяет существенно повысить точность оценки фазы сигнала синхронизации за счет.исключения влияния нормальных ошибок и уменьшения вероятности аномальных ошибок на выходе блока оценки сигнала синхронизации 12.

Формула изобретения

Дискриминатор задержки огибающей и фазы несущей по авт. св. N 4 1 681 8, зоне фазовой характеристики нормальные ошибки фазы сигналя синхронизации не зависят от парязитного смещения рабочей точкиЬ Р относительно нулевого положения.

Однако, дпя минимизации вероягности появления аномальных ошибок на целое число периодов частоты синхронизации, вызываемых "перескоками" рабочей точки фазового детектора из-за воздействия фазовых шумов входного сигнала, необходимо удерживать рабочую точку фазового детек- тора в области нулевых рассогласований. то достигается с помощью управляемого фазовращателя 20, выравнивающего фазовую характеристику узкополосного фильтра 8 относич ельно фильтра 7. При этом в качестве управляющего сигналя фазовращятеля 20 используется.низкочастотная составляющая Bl- ходного сигнала фазового детектора 9, выделяемая низкочастотным фильтром 22

Тираж /О,с Д Поfl11 пcное