Устройство для вывода данных из управляющей цифровой вычислительной машины на обьекты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Сощиалистимееких

Республик (»}507865 (61) Дополнительное к авт. свнд-ву (22) Заявлено14.О8.74 (21) 2О52445/18-24

c: присоединением заявки № (23} Приоритет (43) Опубликовано25.ОЭ.76. Ьюллетень № 11 (45} Дата опубликования описания, 22.О4.76

2 (51) М, Кл.

G 06 Р 3/OÎ

Госудвротвеииый иомитет

Совете Министров СССР по делам изооретений и открытий (53} УДК 681.327.21 (088.8 }

А, П. Гульденбальк, Л. П. Козлов, В. Г. Колосов, Н. И. Колосова, B. Ф. Мелехин и В. В. Чалдыкин (72) Авторы изобретения

Ленинградский Ордена Ленина политехнический институт им. М, И. Калинина (71) Заявитель (54} УСТРОЙСТВО ДЛЯ ВЫВОДА ДАННЫХ ИЭ УПРАВЛЯВШЕЙ

БИФРОНОЙ ВЫЧИСЛИТЕЛЬНОЙ МАКИНЫ HA ОБЪЕКТЫ

Изобретение касается вычислительной техники.

Известны устройства, содержащие накопитель с адресными и информационными шинами, блок у="иления, выход которого через блок формирования сигналов записи соеди нен с информационными шинами накопителя, Одной из существенных задач системы связей является осуществление развязки по

;постоянному току цифровой вычислительной машины (.3ВМ} и внешних блоков.

Известны устройства, в которых такая развязка осуществляется с помощью оптронов, управляемых от элементов потенциального типа.

Другой задачей си темы связей является преобразование сигналов. При связях

ПВМ с объектом, исполнительными и индикационными устройствами обычно требуется сигнал релейного типа: замкнутый либо разомкнутый контакт, наличие либо отсутствие постоянного тока в выходной цепи. Наиболее часто такое преобразование выполняется статистическими регистрами с усилителями на выходе.

В известных устройствах для хранения

:выводимой информации используются регистъ.ры, либо буферная память, что приводит _#_ повьтшентпо сбъема используемого оборудо, вания и сниженито надежности.

Для повышения экономичности и надежности предлагаемое устройстве содержит ,коммутаторы цо числу каналов вывода дан ных, транзисторные ключи с импульсными, тО,трансформаторами по числу каналов выводи мых данных в каждом канале и распределитель импульсов, выход которого подключен к управляющим входам коммутаторов и к адресным шинам группы ячеек накопителя, И информационные шины- которых, включенные последовательно с. информационными шинами других ячеек накопителя, через блок усиле ния соедитепьт со входами коммутаторов, выход каждого из которых соединен с обмот О:.ками записи соответствующих. импульсных трансформаторов, обмотки считывания кото рых соединены последовательно и под.ключены к источнику постоянного тока считыва ния, .выходная обмотка каждого импульснсЯ го трансформатора включена между эмитте3 50 ром и базой соответствующего транзисторного ключа, коллектор и эмиттер которого соединены с соответствующими выходами устро йства, При этом используется то, что в транзисторных ключах с трансформаторным входом время записи (1-2 мксек) может: быть много меньшим, чем время считывания (5O-2ОО мксек), Осуществляя периодичеокое считывание ячеек накопителя магнитного запоминающего блока, хранящих выводимый код, и осуществляя возбуждение соответствующих ключей, можно поддержи вать возбужденные ключи в открытом соотоянии практически непрерывно, Небольшие паузы на время записи для большинства типов нагрузок (электромагниты, лампы накаливания и пр.) не имеют существенного значения. дополнительная загрузка зайоминающего ; -: блока операциями периодического считывания выводимого кода (мак.симальный период считывания можно принять равным времени считывания)„на один канал составляет величину,О,ОО5 О,О2 и во многих случаях1вполне допустима.

Повышение экономичности и. надежности. устройства достигается за счет временного использования общей разрядной системы воспроизведения - записи. Трансформаторы транзисторных ключей обеспечивают гальваническую развязку UBM и внешних объектов. Выход транзисторного ключа можно рассматривать как контакт, который можно включать в любую точку выходной цепи, что расширяет воэможности использования устройства и, следовательно, повышает, его универсальность.

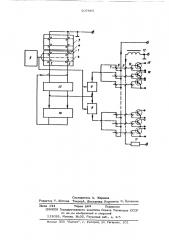

На чертеже дана схема устройства.

Она содержит группу 1 ячеек. накопителя, имеющих информационные шинй 2, общие с остальной частью накопителя 3, адресные шины 4 ячеек 1 подсоединены к выходам распределителя 5 импульсов. К этим же выходам распределителя 5 цодсоединены управляющие входы коммутаторов 6. Число ячеек в группе 1, выходов распреде|ште:и 5 и коммутаторов 6 соответст вуют числу каналов выдачи информации из

UBN. Каждый канал выдачи информации содержит транзисторные ключи с импульсными трансформаторами 7. Число ключей в канале соответствует числу разрядов выводимого кода. Каждый трансформатор 7 содержит обмотку 8 записи, обмотку 9 счи,тывания и выходную обмотку 10. Выходная обмотка 10 каждого трансформатора 7 включена между эмиттером и базой соответ-, ствуюшсго транзистора, Обмотки считывания

9 всех трансформаторов 7 соединены последовательно и включены в цепь постоянного тока, содержащую ограничиваюший резистор

7865 4

11 и индуктивность 12, предназначенную для уменьшения переменной составляющей тока считывания. Обмотки записи 8 трансформаторов 7 через коммутаторы 6 связаны с выходами соответствующих разрядов блока 13 усиления. Выходы блока 13 связаны также с блоком 14 формирования сигналов записи, выход которого соединен с шинами 2, Цифрами 15 и 16 обозначены выходы устройства.

l5

ЯО

И

39

46

ЬО

6О

Работа устройства происходит следукнцим образом, Подлежащие выводу из UBM коды переписываются в соответствующие ячейки группы 1 накопителя, после чего из управляющего устройства периодически запускается распределитель 5 импульсов. Первый выходной импульс распределителя 5 считывает первую ячейку из группы 1 выделенных ячеек накопителя и возбуждает коммун, татор 6 первого канала. В результате считанный иэ ячейки код через усилители воспроизведения блока 13 и коммутатор 6 в виде импульсов тока поступает в .обмотки. записи трансформаторов 7 первого канала, а также записывается в регистр числа блока 14 .и далее вновь записывается в ту же ячейку накопителя. Магнитодвижущая сила (м. д. с.), создаваемая импульсом тока в обмотке 8 превышает м. д. с„создаваемую- постоянным током, протекающим по обмотке 9. Вследствие этого происходит церемагничивание сердечников трансформаторов тех разрядов, где была считана единица . После окончания импульсов записи происходит считывание ключей постоянным током. Во время считывания величина элекэ родвижущей силы (э. д.,) на обмотке 1О имеет .сравнительно малую величину, равную напряженшо на открытом переходе эмнт тер - база. Это обуславливает сравнительно медленное перемагничивание. сердечника трансформатора 7 при считывании. Bo время. считывания транзисторы тех ключей, в трансформаторы которых была произведена запись, находятся в режиме насыщения.. ранзисторы тех ключей, на входы которых импульсы записи не поступали, находятся в режиме отсечки. Для работы устройства существенно различие времени перемагничивания сердечника трансформатора 7 при записи (С ) и при считывании (C ).

При записи э. д. с., наводимая на обмотке

1О, не должна превышать предельно допустимых значений напряжений коллектор-база и эмиттер-база„

Следующий (второй) импульс считывания распределителя 5 считывает вторую ячейку из группы 1 и возбуждает коммутатор 6 второго канала. Считанный код возбуждает транзисторные ключи второго

5 канала, а также через регистр числа блока 14 вновь регенерирует в линейке накопителя. После считывания последней ячейки в группе 1 и передачи информации на ключи последнего Ф »го канала распределитель считывает снова первую ячейку и передает ее содержимое н,". ключи первого канала и так далее. :Для того, чтобы обеспечить квазинепрерывный режим ра боты транзисторных ключей и каналах выдачи с минимально необходимыь и .интервалами на время записи (В ) период Т работы распределителя 5 должен р удовлетворять неравенству Т р Г, а

I интервал Т„.:мемеду двумя соседними им

,,пульсами считывания распределителя 5 дол:жен быть не более Y+ / . При этом ,относительная загрузка (® ) разрядной! ! системы воспроизведения - записи опера пнями по выдаче информации из ШЗМ сос тавляет: Kú Я- О С 1

1 где Т - время обращения к памяти, о включающее время считывания и записи в ячейку памяти, и - число каналов выдачи.

Формула изобретения

Устройство дла вывода данных иэ управ ляюшей цифровой вычислительной машины

О-865

1 на объекты, содержащее накопитель с адрес, ными и информационными шинами, блок уси:ления, выход которого через блок формиро,вания сигналов записи соединен с информа5 ционными шинами накопителя, о т л и ч а1ю ш е е с я тем, что, с целью повышения экономичности и надежности устройства, мю .содержит коммутаторы по числу каналов вывода данных, транзисторные ключи с им,ïóëüñíûìè трансформаторами по числу раз рядов выводимьж данных в каждом канале и распределитель импульсов, вьжод.которого: подключен к управляющим входам коммутаторов и к адресным шинам группь1 ячеек

5, накопителя, информационные шины которых, | включенные последовательно с, .информапион1ными шинами других ячеек накопителя, че» рез блок усиления соединены со входами коммутаторов, выход каждого из которых соединен с обмотками записи соответствую

1щих импульсных трансформаторов, обмотки ! считывания которых ооедиконь последовательно и подключены к источнику постоянного

,тока считывании, выходная обмотка каждого

» импульсного трансформатора включена ман»

1 ду эмиттером и базой соответствующего

,транзисторного ключа, коллектор и эмиттер

l которого соединены с соответствующими выходами устройства.

5О7865

Составитепь- A. Жеренов

Редактор Т. Шагова Техредл. Демьинова Корректор И, Бугакова

Заказ l44 Тираж 864 Подписное

ЦНИИПИ Государствеиногс комитета Совета Министров СССР о де .лм изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ЛИП Патент, г. Ужгород, уп. Гагарина, 1О1