Устройство для определения среднеквадратического отклонения

Иллюстрации

Показать всеРеферат

-с.

,« I

«

О П И С А Н И E

ИЗОБРЕТЕН ИЯ

{> ц 5 07.878

Союз Советских

Социалистических

Республик

{61) Дополнительное к авт; свил-еу (22) 3аявлЕно 23.09.74(2l) 2062044/18-24 (51) М. Кл.

G 06 O 7/52; б 01 В 19 02 с присоединением заявки

Гвсударственнь1й комитет

Соввтв таиннстрав СССР пв делам изобретений и вткрь«тий (23) Приоритет (43) Опубликовано 25.03.76Бюллетень № 11 (45) Дата опубликования описания20.05.76 (53) УДК ,681.333;51 9.2 (088.8) (72) Автор изобретения

А. Г. Быков т7к) Заявитель

Калининградский машиностроительнЬЙ завод

{ Московская обл. ) { 54) УСТРОИСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО

ОТКЛОНЕНИЯ

Изобретение относится к аналоговой вычислительной технике. и может быть применено для определения (вычисления) среднеквадратического отклонения случайного процесса, заданного в виде напряжения,:. 5

Известны устройства для вычисления среднеквадратического отклонения функции времени, заданной в виде напряжения.

Известно устройство для,определениясреднеквадратического отклонения, содержащее р

«блок управления, подключенный к входу устройства, первый интегратор, подключенный входом к источнику постоянного напряжения, а выходом — к входу второго интегратора, компаратор> соединенный выходом с входами д сброса первого и второго интеграторов, тре- тий интегратор.

Погрешность вычислений в известном устройстве зависит от погрешности коэффициентов преобразователя двух основных уз- 20 пов; квадратора и корнеизвлекателя, Цепь изобретения — повышение точности вычислений.

Для этого предлагаемое устройство содержит четыре управляемых переключателя 25 и блок запоминания уровня напряжения, notlкпюченный к выходу первого переключатЕля входы которого . соединены соответственно!

I с входом и выходом, второго интегратора, «первый вход компаратора йодключен к вы»

I ходу второго переключателя, входы ко:торого соединены соответственно с вы, ходами первого и второго интеграторов, втдрой вход компаратора к выходу третьего пе реключателя, входы которого .соединены. со-. ответственно с входом устройства и с выхо дом третьего интегратора, вход которого соединен с первым выходом четвертого перекйючателя второй выход которого подключен к Bbtxo

I ду устройства, а вход-к выходу блока запомина . ния уровня напряжения, вход сброса которого со- единен с выходом компаратора, блок управлений подключен к входам переключателей.

Благодаря этому функции квадратора и корнеизвпекателя совмещаются, устройство значительно упрощается и повышается точность вычисления.

«

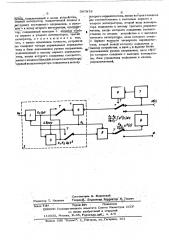

На чертеже изображена блок-схема пред

« пагаемого устройства.

Устройство содержит интегратор 1, квад1507878 нита

Полученное напряжение U> поступает. щ на второй интегратор 3 квадратора 2 и, вновь интегрируется. При этом ин о

R. инт о

"()= Аит= К, )О . <"

Компаратор выдает импульс сброса на оба интегратора в квадраторе 2 и фиксирующий импульс на блок запоминания уровня нап- М ряжения 5. Этот процесс интегрирования и сброса периодически. повторяется.

Иэ формулы (3) время 6 между двумя фиксирующими импульсами оказывается рав1 ным

=KV<= р .

1 о и, ° (9) U =u .„-, sex т. 0(.,)Ю=6,,О) т. е, напряжение на входе интегратора 1 в

Э6 момент 4, а следовательно, и на выходе, блока 5 будет пропорционально среднеквадратичному значению входного сигнала. Из (10) следует, что коэффициент пропорционам

Ъ льности

46 ат (ю

Ъ не зависит от коэффициента преобразования квадратора и корнеиэвлекателя в отличие

45 от существующих приборов.

Независимость коэффициента преобразователя и всеГо устройства в целом от коэффициента преобразовайия двух важнейших узлов значительно повышает точность вычис56 ления среднеквадратического значения.

"Предлагаемое устройство для вычисления среднеквадратического значения функции времени может быть применено при контроле систем автоматического регулирования .

55 для оценки собственных шумов и помех, действующих в контуре управления.

Формула изобретения

Устройство для определения среднеквадра-.

66 тического отклонения содержащее блок управ ратор 2, интегратор 3, компаратор 4, блок запоминания уровня напряжения 5, интегратор 6, блоки управления 7 и 8.

Устройство работает следующим образом.

Постоянное напряжение U интегрируется первым интегратором 1 квадратора 2

Одновременно напражейие Бинт: поступа ет на первый вход компаратора 4, где сравнивается с входным сигналом.

В момент равенства х

1 х U,К1 а максимальное напряжение на выходе вто;рого интегратора 3, фиксируемое в блоке запоминания уровня напряжения 5, получается.йодСтановкой,4) в (2) в виде макс (V )=и к U tx - U Я ) к

Инта i а ь а UR

6 о 1

Напряжение с блока 5, пропорционально квадрату преобразуемой функции, поступает на вход интегратора 6.

Напряжение на выходе интегратора 6 к моменту Т от подачи преобразуемого напряжения на вход будет -.) U «)М. (e) р. у. т . . инт (К О 6 ь

В момент Т блок управления 7 выдает сигнал на блок управления 8 переключателями, которые перебрасываются в.положе> ние, противоположное указанному на чертеже, В результате такого переключения квад.ратор 2 ставится в режим корнеизвлекателя, на его вход, вместо преобразуемого подается напряжение с выхода интегратора, .соответствующее (6), на вход блока 5 вместо напряжения со второго интегратора

3 подается напряжение с первого интегратора 1.

Оба интегратора (корнеизвлекателя) рабоо тают в прежнем режиме, как и раньше компаратор 4 выдает импульс сброса и фиксации в момент равенства поданных на его вход напряжений, т. е. когда > унт инт к,к,,/ >> > > -K к v

>> к о " 1aa». (1> о

Иэ (7) время с от подачи Т до выдачи очередного импульса с компаратора бу, дет равно

1 . т р.

t»= — U a, / u < „>И. <в>

В это время на первом интеграторе 1, а следовательно, и на блоке 5 будет напря>жение

Если принять (что всегда возможно) к =и /Т, (.10) то из (9) следует, что,, 5

Яенйя, подключенный к входу устройства,,пелрвый интегратор, подключенный входом к

;источнику постоянного напряжения, а выхо. уыу, дом - к входу второго интегратора, комйауат тор, соединенный выходом с, входами сбро-. са первого и второго интеграторов, третий интегратор, о т л и ч а ю ш е е с я тем, ;что, с целью повышения точности, устройств во содержит четыре управляемых переключа теля и блок запоминания уровня напряжения, подключенный к выходу первого переключа:. теля, входы которого соединены соответст)

)венно с входом и выходом второго интегратора, первый вход компаратора подключен к выходу

7878 второго переключателя, вкоцы которого соединераи соответственно с выходами первого и второго интеграторов, второй вход компара

;тора подключен к выходу третьего,переклю5 чателя, входы которого соединены соответ ственно со входом устройства .и с выходом

1 . третьего интегратора, вход которого соеди с первым выходом четвертого переключа-I тели, второй выход которого подключен к (Выходу устройства, а axon - к выходу блока запоминания уровня напряжения, вход сброса которого соединен с выходом компаратора, блок управления подключен к входам переключателей.

-.Составййтюлйв В Жовинский

Редактор Т. Иванова . Гехред А. Демьянова Корректор И. Гоксич

Заказ 316< Тираж 86Ч Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаянаб., A. 4/5

Филиал ППП "Патент, г Ужгород, ул. Гагарина, 101