Устройство формирования импульсных последовательностей

Иллюстрации

Показать всеРеферат

Оll ИСАНИЕ 5о79л

ИЗОБРЕТЕН ИЯ

Союз Советских

Соцналистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву2 (51) М. Кл.

Н 03 К 3/78 (22) Заявлено 28.03.73(21) 1900758/26-21 с присоединением заявки №

Гасударственный номнтет

Совета Мнннстров СССР по делам нэобретеннй н открытнй (23) Приоритет (43) Опубликовано 25,03.76)Бюллетень Ю ll {53) УДК 621.374 (088.8 ) (45) Дата опубликования описания 28.04.76 (72) Автор изобретения

E. Б. Алексеев (71) Заявитель (54) УСТРОЙСТВО ФОРМИРОВАНИЙ ИМПУЛЬСНЫХ

ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к области импульсной техники и может быть использовано в вычислительных и радиоизмерительных KGM плексах, е Известно устройство формирования им.пульсных последовательностей, содержащее каскады, каждый из которых содержит транзистор, в эмиттерную uem которого включен диод с накопителем заряда, и линию задержки, выход которой соединен с базой транзистора.

НеАосТВТКоМ такого устройства является большая громоздкость для случаев формирования последовательностей с большим числом импульсов в пачке, так как число импульсов в последовательности определяет число каскадов формирования.

Бель изобретения - увеличить число импульсов формируемой последовательности и обеспечить возможность регулирования длительности и скважности импульсов в последовательности.

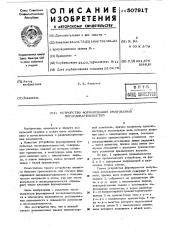

Это достигается тем, что в каждый каскад дополнительно введен транзисторный усилитель, причем коллектор транэисзистора,в эммитерную цепь которого включен диод с накоплением заряда, соединен со входом транзисторного усилителя непосредственно, а со входом линии задержки — через резистор, причем вход линии задержки объединен с выходном транзисторного усилителя предыдушего каскада, На фиг. 1 приведена принципиальная у схема предлагаемого устройства; на фиг.

2 и 3 — диаграмма напряженней в различных точках схемы.

Схема устройства формирования импульсных последовательностей содержит 2 каскада, причем вход первого элемента задержки 1, собранного на транзисторе типа п,-р - и, диоде с накоплением заряда, непосредственно связан с источником запускающих импульсов, а через реэистор, рр . 2 — со входом первого транзисторного усилителя 3 на транзисторах типа и-р-л. и

Г-и,-р и с коллектором транзистора 4 ти па к,- р-и эмиттер которого подсоединен к катоду диода 5 с накоплением заряда, 35 .анод которого подключен к общей шине, 507 - ) 7

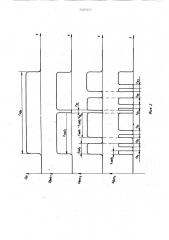

l5 где Еъ — время задержки сигнала элементом задержки в К вЂ” том каскаде; — длительность фазы высокой обратной проводимости диода с накоплечием заряда в эмиттерной цепи транзистора к - того ,И каскада; †длительнос входного сигнала;

ВХ вЂ” число каскадов, то при действии каждого импульса на входе устройства на его выходе формируется щ последовательность импульсов со скважностью 2 (см. временную диаграмму, соответствующую и 3, на фиг. 3).

Во время фазы рассасывания заряда в базе диода 5 с накоплением заряда, накал

ЭО лекторе транзистора 4 напряжение равняет.ся сумме напряжения насыщения коллекторэмиттер и напряжения на диоде 5. Чтобы это напряжение не усиливалось усилителем

3, последний настроен на срабатывание по определенному уровню входного сигнала введением дополнительного смещения на эмиттер-базовом переходе первого транэис тора, 4Ъ

Поступающий на вход первого каскада устройства сигнал положительной полярности через резистор 2 поступает на вход усилителя 3. Усиливаясь (коэффициент усиления, приведенный ко входу каскада, равен единице), сигнал поступает на вход следующего каскада. Одновременно сигнал, задерживаясь элементом задержки 1, поступает через резистор 8 на базу транзистора 4 и открывает его. В этот момент сигнал на входе усилителю 3 уменьшается практически до нуля; При этом через диод

5 начинает протекать обратный ток, происходит рассасывание заряда в его базе. По окончании длительности фазы высокой Обрат ной проводимости диода 5 с накоплением заряда, его обратное сопротивление резко восстанавливается, напряжение на коллекторе транзистора 4, а следовательно, и на выходе усилителя 3 резко возрастает, прак- 49 .тически до первоначального значения. Таким образом, на выходе первого каскада формируются два импульса с временем сдвига между ними, равным длительности фазы высокой обратной проводимости диода 5, причем длительность первого из них равна t времени задержки элемента 1.

При поступлении этих импульсов на второй каскад совершенно аналогично из каждого из них формируются на выходе по два импульса с временем сдвига между ними, определенным длительностью фазы высокой обратной проводимости диода с накоплением заряда, включенного в эмиттерную цепь трен эистора во втором каскаде, причем длительность каждого первого из них определяется временем задержки. сигнала элементом заде жки во втором каскаде.

Таким обраэЬм, на выходе каждого кас» када происходит удвоение частоты следоваУстройство формирования импульсных последовательностей, каждый каскад которого содержит транзистор, в эмиттерную цепь которого включен диод с накоплением заряда, и линию задержки, выход которой соединен с базой-транзистора, о т л ич а ю щ е е с я тем, что, с целью увеличения числа импульсов формируемой последовательности и воэможности регулировки скважности, в каждый каскад дополни тельно введен транзисторный усилитель, причем коллектор транзистора, в эмиттерную цепь которого включен диод с накоплением заряда, соединен со входом транзисторного усилителя непосредственно, а

I ( со входом линии задержки - через рези- . стор, причем вход линии задержки соеди-, .нен с выходом транзисторного усилителя

yj предыдущего каскада.

1!..*ыхс.д первого транзистора усилителя 3 соединен со входом второго элемента задержки 6, эмиттер транзистора 4 через резистор 7 подключен к источнику F. прямого смещения диода 5 с накоплениеМ заряда, a его база через резистор. 8 связана с выходо.A первого элемента задержк, l. Второй каскад выполнен аналогично.

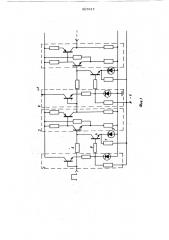

На диаграммах приняты следующие обозначения: Ц ° ° — импульсы на входе ых 1 усилителя 3 первого каскада; х, то жЕ ДЛЯ ВТОРОГО КаСКаДа; 0 ых — тО же для третьего каскада (на схеме не Воказан) U „- импульсы на выходе усилителя

Ьц последнего (третьего каскада) .

Предлагаемое устройство работает следующим образом.

В исходном состоянии транзистор 4 закрыт, а через диод 5 протекает прямой ток; накапливая заряд в его базе.

4 ния импульсов, и, например, на выходе трехкаскадного устройства формируется при действии на его входе одного импульса последов ательн ос ть из 8, импульсов (см. Ug „х ча фиг. 2) .

Регулированием времени задержки элементов задержки и длительности фазы высокой обратной проводимости 1д осуществляется регулировка длительности и саважности импульсов в последовательности.

B частности, если

За.б.к + z ) у д

Формула изобретения

5 )79) 7

Составитель М. Жуков

Редактор О. Стенина ТехредО. Луговая Корректор 3. Фанта

Заказ 178 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/S

Филиал ППП "Патент", r, Ужгород, ул. Гагарина, 101