Масштабный преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (») 507927 (61) Дополнительное к авт. свид-ву— (22) Заявлено 24.05.74 (21) 2027 27 6/26-21 с присоединением заявки М (23) Приоритет (43) Опубликовано26.03.76.Бюллетень ¹ 11 (45) Дата опубликования описания 14.04.76 (51) М. Кл.

Н 03 К 13/02

Госурарстванный коглнтет

Совата Чинистрав СССР по далам иваоратаний и открытий (53) УДК 621.317.

361(088 8) (72) Авторы изобретения

А. А. Богородицкий, Э. П. Дзисяк и A. A. Скорляков

Пензенский филиал Всесоюзного научно-исследовательского технологического института приборостроения (71) Заявитель (54) МАСШТАБНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области цифровой измерительной техники и может быть использовано при создании масштабных преобразователей интервалов времени.

Известные масштабные преобразователи содержат оперативный и запоминающий счетчики, состоящие из последовательно соединенных через схемы сборки декад, и селектор тактовых импульсов.

Однако в этих устройствах необходимо 10 использовать реверсивный счетчик, что усложняет их и требует увеличения объема оборудования.

Целью изобретения является упрощение преобразований. 15

Это достигается тем, что устройство снабжено триггерами и ключами по числу декад запоминающего счетчика, при этом выход схемы сборки, подключенной к выходу стаошей декады оперативчого счет- 20 чика, соединен с одним a входов всех триггеров, кроме триггера младшей декады, вход которого связан с одним из выходов селектора тактовых импульсов, вторые входы всех тргггеров подсоединены к 25 выходам соответствующих декад запоминающего счетчика, а вь. ходы триггеров через ключи соединены со входами соответствующих схем сборки оперативного счетчика.

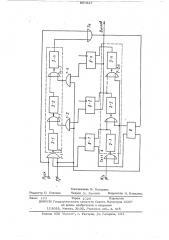

На чертеже представлена блок-схема устройства.

Оно содержит ключи 1-1 1- и, оперативный счетчик 2, включающий в себя декады 3-1 — 3- т, запоминающий счетчик 4, включающий в сеоя декады 5-1—

5-п, -триггеры 6-1 — 6- и, схемы сборки 7-1 — 7-2.г, и селектор тактовых импульсов 8.

Устройство работает следующим образом.

Вначале триггер 6-1 находится в таком состоянии, при котором управляющий потенциал с его выхода открывает ключ 1-1 по соответствующему входу, а управляющие потенциалы триггеров 6-2 — 6- тъ закрывают соответственно ключи 1-2 — 1- Tl

В запоминающий счетчик 4 заносится код

М преобразуемого интервала времени Т., По команде "пуск" открывается ключ

1-1 t импульсь! частоты -„"g начинают пDсту гать на вход опе ратив н ого счетчика 2.

807с; r7

Одновременно селектор 8 тактовых импульсов запускается, выделяя десять импульсов частоты f<, и перебрасываются триггеры 6-2 — 6- и в состояние, при котором открываются ключи 1-1 — 1- .

Импульсы частоты f поступают через схемы сборки 7-1 — 7-2 т на счетные входы декад 5-1 — 5- зъ запоминаюшего счетчика 4.

При просчете 10 — N импульсов, где

N- — код в декаде 5- запоминаюшего

Ъ счетчика 4, импульс переполнения декады

5- ъ перебрасывает триггер 6- ъ, закрывая тем самым ключ 1-> . 3a время, в течение которого открыт ключ 1-, через него проходят 10- М импульсов и зафиксируют в декаде 3- оперативного счетчика 2 дополнительный код 10- И числа

Так происходит перепись кодов всех декад, кроме младшей, Код младшей декады 5-1 запоминаюшего счетчика 4 непосредственно не переписывается в первую декаду 3-1 оперативного счетчика 2, а управляет ключом 1-1.

По команде "пуск" ключ 1-1 открывается и через него на вход оперативного счетчика 2 начинают поступать импульсы частоты f . При просчете 10- Yj, импульсов с выхода селектора тактовь.х импульсов 8 сигнал переполнения первой декады

5-1 запоминающего счетчика 4 перебрасывает триггер 6-1, закрывая тем самым ключ 1-1, Лишь десятый импульс с выхода селектора 8 вновь перебросит триггер

6-1 и откроет ключ 1-1.

В момент переполнения оперативного счетчика 2 импульс переполнения, воздействуя на триггеры 6-2 — 6- с, перебрасывает их. При этом ключи 1-2 — 1- и открываются, вновь запускается селектор тактовых импульсов 8 и весь процесс повторяется.

За счет применения такой схемы удается устранить паузу между воспроизводимы...v. и нHт ер в а л а м. и в р еeм. еeнH и, совместив процесс переписи кода с процессом воспроизведения преобразуемого интервала. Кроме того, при переписи кодов не возникает переходных

10 процессов, что совместно с устранением доп олните ль ной нагрузки на пере счетные схемы счетчиков позволяет максимально использовать их быстродействие, а отсутствие реверсивного счетчика дает возмож15 ность уменьшить объем оборудования, 1

Формула изобретения

20 14асштабный преобразователь, содержаший оперативный и запоминаюший счетчики, состояшие из последовательно соединенных через схемы сборки декад, и селектор тактовых .импульсов, о т л и ч а25 ю ш и и с я тем, что, с целью упрошения преобразований, он снабжен триггерами и ктцочами по числу декад запоминаюшего счетчика, при этом выход схемы сборки, подключенной к выходу старшей

30 декады оперативного счетчика, соединен с одним из входов всех триггеров, кроме триггера младшей декады, вход которого связан с одним из выходов селектора тактовых импульсов, вторые входы всех триггеров подсоединены к выходам соответствуюших декад запоминающего счетчика, а выходы триггеров через ключи соединены со входами соответствующих схем сборки оперативного счетчика.

507927

Составитель В. Назарова Гехред М. дикович Корректор Н. Ковалева

Редактор О. Степина

Заказ 133 ТНр G2K Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий C 113035, Москва, K-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Гагарина, 101