Декодер сверточного кода

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

{11) 507929

К АВТОеаО4ОММ СВИдН ИДЬСТВу (61) Дополнительное к авт. свид-ву (22) Заявлено 26.02.74 (21) 2002494/26-9 с присоединением заявки Ме (23) Приоритет (43) Опубликовано 25.03.7616юллетень М 11 (45) Дата опубликования описания 16.04.76

Государственный номнтет

Совета Инннотроа СССР ао делам нзооретеннй н отнрмтнй (53) УДК

6 21. 394 (088.8) (72) Авторы изобретения

А. Э. Нейфах и Н. А. Александров (71) Заявитель (54) ДЕКОДЕР СВЕРТОЧНОГО КОДИРОВАНИЯ

Для этого дополнительно введены регистр для зашиты информации, счетчик отсутствия ошибок, триггер состояния, два элемента ИЛИ и ключ, при этом вход регистра для защиты информации подключен к выходам сумматоров для исправле» ния ошибок, выходы синдромных регистров соединены через первый элемент ИЛИ с одним входом триггера состояния, выход 0 которого подключен к стирающему входу регистра для защиты информации, запрещающему входу блока для формирования логических функций и разрешающему входу ключа, к другому входу которого че15 рез второй элемент ИЛИ подключены выходы сумматоров для формирования синдрома, а выход ключа соединен с входом счетчика отсутствия ошибок и выходом первого элемента ИЛИ, причем выход

20 .счетчика отсутствия ошибок соединен с другим входом триггера состояния, второй выход которого подключен к другому входу элемента совпадения, На чертеже приведена структурная

25 электрическая схема декодера сверточноИзобретение относится к технике передачи данных и может использоваться при передаче дискретных сообщений свер- . точными кодами по каналам связи с шумом.

Известен декгдер сверточного кода размерности {., b-тп.), содержащий синхронизатор;,;ементарн ого блока, соединенный;.-,".ез буфер и регистры информа,цион . . и проверочных символов с вхор-,,. тп. сумматоров формирования син,.рома и b-m сумматоров исправления ошибок, при этом регистрь. проверочных символов соединены через элементы совпадения с входом синдромных регистров, к которым подключен блок для формирования логических функций.

Однако известный декодер не обладает высокой корректирующей способностью и не устраняет эффекта размножения ошибок.

Целью изобретения является повышение корректирующей способности декодера и устранение эффекта размножения ol бок. (51) М. Кл.

Н 03 К 13/17

Н 04 L 1/10

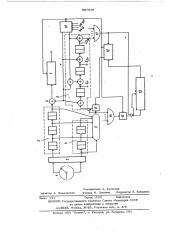

© 507929 го кода размерности (2, 1), исправляющего пачки ошибок длиной 2I, где r равно, например, двум.

Декодер сверточного кода размерности (b, Ь- m )),, нHа п р иHмMеeр p ((22, 1) содержит син- 5 хронизатор элементарного блока 1, соединенный через буфер 2 и регистры информационных и проверочных символов 3 и 4 с входами сумматора 5 для формирования синдрома и сумматора 6 для исправления 10 ошибок, выход которого подключен к входу регистра 7 для зашиты информации, элемент совпадения,8, через который сумматор S соединен с входом синдромного ре гистра 9, к-которому подключен блок 10 И для формирования логических функций и элемент ИЛИ 11, через который выход синдромного регистра 9 соединен с одним входом триггера состояния 12, à его вь.— ход подключен к стирающему входу реги- хп стра 7, запрещающему входу блока 10 и разрешающему входу ключа 13, к другому входу которого через элемент ИЛИ 14 под« ключен выход сумматора 5, а выход ключа 13 соединен с выходом элемента ИЛИ

11 и входом счетчика отсутствия ошибок

15, выход которого соединен с другим входом триггера 12, второй выход которого подключен к другому входу элемента совпадения 8.

Для общего случая сверточного кода размерности (Ь, b - тл. ) декодер содержит по m сумматоров 5 для формирования синдрома, выходы которых подключены к входам элемента ИЛИ 14, элемента совпадения 8 и синдромных регистров 9, вы-. ходы которых подключены к входам элемента ИЛИ 11, а также b- m сумматоров 6 для исправления ошибок, Декодер работает следующим образом.

Логическая функция Р1 5>> 5о (5ьг 5„), снимаемая с выхода. блока 10 для формирования логических функций, исправляет информационные символы кода в сумматоре 6 для исправления ошибок и производит обратное воздействие на синдромный регистр

Логическая функция Fq = S „(5гт, S„)(5„.ß снимается с другого выхода блока 10, используется для изменения содержимого синдромного регистра 9.

Нулевой сигнал "признак ошибки" поступает с сиидромного регистра 9 на вход элемента ИЛИ 11, если комбинация ошибок на входе декодера не может быть исправлена.

Сигнал "признак ошибки" сбрасывает счетчик отсутствия ошибок 15 и перебрасывает триггер состояния 12 во второе

1 состояние. Это приводит к закрытию элемента совпадения 8, блокировке блока 10 и открытию ключа 13.

Каждый не нулевой сигнал с выхода сумматора 5 после этого устанавливает счетчик отсутствия ошибок 15 в начальное положение.

Если в течение К-1 тактов подряд отсутствует сигнал с выхода сумматора 5, то сигнал с счетчика отсутствия ошибок 15 перебрасывает триггер 12 в первое состояние и декодер возвращается в исходное состояние, в котором он не более, чем через К тактов после переброса триггера состояния 12 может исправлять ошибки.

Регистр 7; имеющий К разрядов, предотвращает поступление неисправленных ошибок к потребителю перед обнаружением ошибки, Формула изобретения

Декодер сверточного кода размерности (b, b-m ), содержащий синхронизатор элементарного блока, соединенный через буфер и регистры информационных и проверочных символов с входами m сумматоров для формирования синдрома и Ь- m сумматоров для исправления ошибок, при этом регистры проверочных символов соединены через элементы совпадения с входом синдромных регистров, к которым подключен блок для формирования логических функций, отличающийся тем, что, с целью повышения корректирующей способности декодера и устранения эффекта размножения ошибок, дополнительно введены регистр для защиты информации, счетчик отсутствия ошибок, триггер состояния, два элемента ИЛИ и ключ, при этом вхОц регистра для защиты информации подключен к выходам сумматоров для исправления ошибок, выходы синдромных регистров соединены через первый элемент ИЛИ с одним входом триггера состояния, выход которого подключен к стирающему входу регистра для защиты информации, запрещающему входу блока для формирования логических функций и разрешающему входу ключа, к другому входу которого через второй элемент ИЛИ подключены выходы сумматоров для формирования синдрома, а выход ключа соединен с входом счетчика отсутствия ошибок и выходом первого элемента ИЛИ, причем выход счетчика отсутствия ошибок соединен с другим входом триггера состояния, второй выход которого подключен к другому входу э.цементов совпадения.

507929

Составитель А. Кузнецов

Техред М. Ликович Корректор Н. Ковалева. едактор А, Зиньковский

Филиал ППП Патент, г. Ужгород, ул. Гагарина, 101

Заказ 133 Тираж 1029 Подписное

UHHHHH Государственного комитега Совета Министров СССР по делам изобретеннй и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/S