Счетчик с параллельным переносом

Иллюстрации

Показать всеРеферат

Союз Советских

Ео иалистииесних

Республ >н (61) Дополнительное к авт. свид-ву (22) Заявлено 30.12,74(21) 2089307/26-21 с присоединением заявки № (23) Приоритет (43) Опубликовано25.03.76.Бюллетень №11

Н 03 К 23/02

Государственный комитет

Совета Министров СССР оо делам изобретений н OTKpblT»H (53) УДК

681.374,32(088 8) (45) Дата опубликования описания 14.04.76 (72) Авторы изобретения

И. М. Лазер, П. И. Овсишер, B. А. Шубарев, Ю. С. Крылов и С. Й. Шац (71) Заявитель (54) СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ

Изобретение относится к вычислитель ной технике и автоматике.

Известен счетчик с параллельным переносом, содержаший Я разрядов, каждый из которых содержит триггер памяти и два коммутационных триггера, образуюших Т-триггер и выполненных на логических элементах И-HE/ÈËÈ-НЕ, при этом счетные входы коммутационных триггеров 1 — М разрядов соединены с первым выходным каскадом источника счетных импульсов, а счетные входы коммутационных триггеров (М+1) — Я разрядов — со вторым выходным каскадом источника счетных импульсов.

Однако надежность известного устройства невысока из-за наличия опасных состязаний при работе соседних разрядов счетчика от разных выходных каскадов источника счетных импульсов, которые могут привести к сбоям. Кроме того, устранение опасных состязаний снижает бь>стродействие счетчиков.

11елью изобретения является повышение надежности и быстродействия.

С этой целью дополнительный единичный вход первого коммутационного триггера К гого разряда, где К 1, ..., М, соединен с нулевым выходом второго коммутационного триггера этого же разряда, а единичный выход — с дополнительными нулевыми входами коммутационных триггеров (М+ 1)-го разряда.

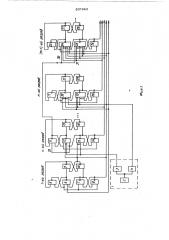

На фиг. 1 представлена электрическая структурная схема счетчика с параллельным переносом, каждый разряд которого построен на основе несимметричного Ттриггера; на фиг. 2 — в ре ме нные д иаграммы работы счетчика с параллельным пере15 носом," на фиг, 3 — электрическая структурная схема счетчика с параллельным переносом, каждый разряд которого построен на основе симметричного Т-триггера.

Счетчик импульсов с параллельным е20 реносом в случае построения его разрядов на основе несимметричного Т-триггера (см.фиг. 1) содержит источник счетных импульсов 1, в который входят формирователь 2 счетных импульсов и вы>

И ходные каскады 3 и 4, Первый разряд счетчика достигается за счет соединения нулевого выхода второго коммутационного триггера )2 -го разряда (элемент 13) дополнительным единичным входом первого коммутационного триггера (элемент 11).

Тогда переход 0 1 на выходе элемента

11 формируется за счет переключения цепочки элементов 13-11, что в два раза уменьшает время задержки в h. -ом разряде сигнала, разрешающего переключение (М+ 1)го разряда, и соответствующим образом повышает быстродействие счетчика.

В случае построения разряда счетчика на основе симметричного Т-триггера (см. у фиг. 3), соответствующие его разряды реализуются на аналогичных элементах

5-28, Й -ый разряд содержит идентичные дополнительные соединения 29-31 между собственными коммутационными ц триггерами и коммутационными .триггерами первого разряда второй части счетчика. Кроме того, разряды счетчика содер-; жат по одному элементу 32-35 образования сигнала переноса, входы которого 5 соединены с единичным выходом первого коммутационного триггера и нулевым выходом второго коммутационного триггера.

Счетчик с параллельным переносом, содержащий Я разрядов, каждый из которых содержит триггер памяти и два коммутационных триггера, образующих Т-триггер и выполненных на логических элементах И-НЕ/ИЛИ-НЕ, при этом счетные входы коммутационных триггеров 1 -М разрядов соединены с первым выходным каскадом источника счетных импульсов, а счетные входы коммутационных триггеров {М+ 1) — N разрядов — со вторым выходным каскадом источника счетных импульсов, отличающийся тем, что, с целью повышения надежности и быстродействия, дополнительный единичный вход первого коммутационного триггера Х -ro разряда, где k = 1, М, соединен с нулевым выходом второго коммутационного триггера этого же разряда, а единичный выход — с дополнительными нулевыми входами коммутационных триггеров (М+1)-го разряда.

507943

3 счетчика построен на логических элементах И-НЕ/ИЛИ-НЕ 5 —: 10,1 k -ый разряд - на элементах 11 —: 16 М-ый разряд - на элементах 17 - „22 и {М+1)-ый .разряд - на элементах 23 - 28.

Работу счетчика рассмотрим начиная м 2ф-1 с (2 — Р )-го счетного импульса (см. фиг. 2). Поскольку этот импульс четный, то в момент t первый разряд устанавливается в 0", а К-ый разряд — в "1" и счетчик переходит в состояние 000 ... 1 к

111 ООО ... Исключение представляет

Случай, когда в качестве h -го разряда используется первый. Тогда первый разряд воспринимает все свойства R. -го разряда, м в частности по (2 — 2 )-му счетному .> импульсу, который в этом случае будет нечетиым, он переключается в еденицу и счетчикк переходит в состояние 1 1 1 ... 1 м000...

По окончании (2 - 2 )-го счетного имм пульса (момент ) Й -ый разряд на выходе логического элемента И-НЕ/ИЛИ-HE

ll вырабатывает нулевой сигнал. В момент

Ф происходит переключение первого разряда в единицу.

Переключения первого разряда, определяемые моментом времени, не могут вызвать неправильных (сбойных) переключений (М+ 1 ) -го разряда, так к ак этому препятствует нулевой сигнал с выхода ло- 30 Ф о р м у л а и з о б р е r е н и я гического элемента И-НЕ/ИЛИ-НЕ 1 1. А в момент времени t 5 . происходят закономерные переключепия разрядов с 1-го по

М-ый, переводящие эти разряды в нулевое состояние, В момент t< закономерно переключается (М+ 1 ) -ый разряд, поскольку к этому моменту на выходе логического элемента И-НЕ/ИЛИ-НЕ 11 k -го разряда нулевой сигнал заменяется на единичный.

Структура h -го разряда, аналогичная структуре всех других разрядов, определяла бы последовательность переключения элементов, в результате которого на выходе логического элемента И-HE/ÈËÈ-НЕ 11 формировался бы переход О- 1, следующим образом: 13-16-15-11. При вь.полнении

Я 1Ь t5 условия — t c g + + g + т 5 5 Ъ Ь Ъ 3 11 где t> - задержка сигнала в гъ -ом элементе, время срабатывания (М+1)-го разряде при обычной структуре я -го разряда увеличивается за счет цепочки элементов

Jt -го разряда. Увеличение быстродействия

507943 ь

i Q

° Ф !

Редактор О, Степина

Заказ 33 Тираж 1029 Подписное

1.11-(1111Г111 Государственного комитета Совета Министров СССР по делам изобретений и открытий

11 3035, Москва, ?К-35, Раушскан наб., n. 4/5

Филиал П1111 "l lûòeíò", r. Ужгоро, ул. Гагарина, 101 ь

1 б!

Составитель М, Аудринг

Texneli М. Ликович Корректор Н. Ковалева