Временной выравниватель каналов для передачи дискретных сигналов

Иллюстрации

Показать всеРеферат

О П И С А H И Е 607948

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено07.06.74 <21) 2032 64/26-9 с присоединениеi; заявки № (23) Приоритет (43) С?иубликовано 2>.0З.7 6.Бюллетень Xv 11 (45) Дата опубликования описания 20.04.7g (5!) М. Кл, НО4 ВЗ:0д

Государственный комитет

Совета Министров СССР по делам изооретений

N открытий (53) УДК О21.ЗО1,Я;?Д (08H. й) (72) Авторы изобретения

А. М. Агапакон и А. М. Ивянов (71) Заявитель (54) ВРЕМЕННОЙ BblPABHHBATEfIb КАНАЛОВ ДЛЯ

ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ (Изобретение относится к технике связи и может использоваться в аппаратуре дпя передачи данных.

Известен временной выравниватепь канапов передачи дискретных сигналов, содержаший управляемую линию задержки, информационный выход которой подключен к анализетору отсутствия выравнивания, узел дляфао зирования каналов и индикатор.

Однако известный временной выравнивао тель каналов для передачи дискретных сиг.налов имеет входной регистр, накопитель и датчик, цикповых импульсов, объем которых значительно возрастает с увеличением допустимого временного сдвига. !5

11епью изобретения является упрошение сопряжения выравниватепя с аппаратурой для передачи дискретных сигналов.

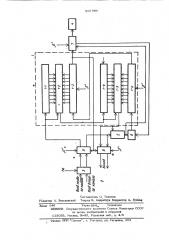

Ддя этого во временном выравниватепе канжов передачи дискретных сигналов введены допопнитепьный анализатор и дваперекпючатепя, выходы узла дпя фазирования .каналов, например двух, подключены к входам первого введенного.переключателя канадов, первый выход которого подкпючен к входу анализатора отсутствия е..н,м.нивпния, а второй выход - к инфор.-тационному входу управляемой линии задержки, к управляюшему входу которой подключен элемент запрета, входы которого соединены с выхо,дами анализатора отсутствия выравнивания и

:дополнительного анализатора наличия выравнивания, соединенного с индикатором, причем один иэ входов анализатора наличия выравнивания подключен к управлявшему выходу управляемой линии задержки, r. другой — квыходу анализатора отсутствия выравиива( ния, при этом первый выход первого перс кпючателя каналов дополнитепьно подключен к первому входу второго введенного переключателя каналов, к второму входу которого подключен информационный выход управляемой пинии задержки, управпяюший выход которой подключен к третьим входам обоих переключателей каналов, при этом управляемая линия задержки содержит уп равляютцие блоки, коммутаторы, m -разрядный регистр сдвига с отводами от каждо3 о (тт + 1) -го таэряда, подкптченными к первому коммутатбру, соединенному с

"т (- З11(:О.л(-("(б1(ОК0,1, 1. Г -РВЗРЯиИЫй(P: л :.-д"-.. "..(тт OT т Лжгтр(О РОЗ С,т(ти(1 тяп>(-(;т(.". (ВТ >pod.ту, ;0;,,т1,(у (а 0 = .. 1((C :ттo(.ттт С В ".r .,(М IПРаВЛ H(ОтЦтт М

Л-;,:.т Э-10 т ттттЬР(;,. PH((0H(lb(P ВХОД ( -. "":(, .10: i:!Э ПС .(",;т, Дтт.(гq И -.(0ВOIO

" "-. - .0H .:питт(3 (ЕИ(Ы К Ит:фсрт...ацтt(ОННО

",„тЦра т ЭМОй,ттттНИ - Зап -Ож-„.;-И

1 ГС .Г0,7 Г",Т -;" O.За: — тспт(.т; —;-.oz.а((К т(т-(., л,.iл т,, .„.От. тр т"(т:0 0 ООГHCТра

J.

--, -,,тт--, К. (, ттт-,т: ттт .т-"„-.ЫХОП КОТО

p"".-(H (Задтартхкт(„ПРИ-.СМт Прае, т л

-.-,—.,(-„ал.-.(а;,(О;,:. ;;,,;-(Цти Зат(эржкн

,n-, т т(т-т":."а, Ы". Од т т " ЗОГО ГОД.т(т-.л-и тэ(ттэ т.(-.- .bo;OÄ",) Чт(саВЛЯЕ(т, тОЙ т-:Г, ь" —.", .,.,,." . > т"., — ЦЕПОЕ ,,п.;",э приведе;(т(структурная(элекс-.,; —. та выравт.—., ".зателн каналов. т- „:Етттто, ; (Оантт(теа тэттв тралаЛОВ дця ттт т таттЬ((: тт,""-, топ СОДЕОЖИТ "тт( т; ., -,т-.;;ЬЛО За,ттэр. (1-. „"т ., т(1(ГЗОРК(ацтиои —;- -т - -Oй ЛОдКПЮЧЕН ", ат(аПИЗато<, „-- .т (;,я зь(рава(1 твоа(-;((я т узетт 3 g)p —. -г...-.„.-,л к;.;т. „ттов и l(H(;(. I;HToo 4;, Вы Оды . л пратт(таз;.=а -; . -о -о для фаз((побаниц а --.: ..,. -Ол.-:,010 ены (i т=,;,onav. первого вве"0 ттэ - КЛ(сттатЕЛ 5 Кат(аттоа ЛЕРВЫИ тт туг ГР ттОПК(ттсттэ(т Y ВХОДтт аиаПИЗЯ . ";, т; (p". .", : тт(ттт ттнтсат;..ттнаттття а RTopoff

- -. (т..-".С(- РМатттт(ОН(О .(У ВХОДУ УПРаВПЯЕ- ттт: тти т зя цетдттткт(т„" тлт)яял я(От((Р му Вхо

:lo1 Ойт лс дключен залре(цта(0(лий блок 6, КОТОРОГО СОЕДт(ттЕНЬ(С ВЫХОДаМИ BHG-

--.-(-эатср=(; отсу-гствття выравнивания т(вве»= -Го-:О а-.талт .затора 7 наличия выравнива-". Ссадине."..-.ного с индикатором 4, причем

-;--((à вхсдов анализатора 7 наличия вы- -т(ттванц1(подклточет(к управляющему выулравляемой линии 1 задержки, а друвь(ходу анализатора 2 отсутствия

Он((((ватт((я, при атом (тервый выходпер:.: -о псрекл очателя 5 каналов лопопнитепь-.,:,кл.о (Он к лервомУ тхолУ второго вве;. С.(ного переключа еля 8 кат(апов, к втоооМ,т ВХОДУ КОТОРОГО ПОДКЛЮт(ЕН 1(НфОРМаЦИОН »

:-".. :: ВЬ(ХОц упраВЛяЕМОй ЙИНИИ1 Задэржкн

- ((Раг(;Я.ОЩИй ВЫХОД КОTOOON ПОДКЛ(ОЧЕН I( —:..ать((..(входам обот(х леректпочатепей 5 и т, т ка-(алов„улравляемая л((нч5("i задержки с;держ((т улравляющий блок, коммутаторы, *" .. Язряднь!Й РегистР 1 -(сдвига с Отво-т ,"аМ::1 СТ КатжДОГО (Л-+ ()-ГO РаЗРЯДа, ПОД. I1o —..ã:11(b((<((1 1<-. первому коммутатору 12, о .—.;";-;Гтт (01(!;..o; ;.. с первь(м 1-3;,тлравляю(((им ,.-" КОМ. И у1-даэ05(дт((Ь(".т ОЕГ(тСТР 1.-4 СдВИГа о-.(:ага. и(от каждого Разряда„лодк((ючен ными к второму ком((у(атору 1 5, соединенному с вторым управляющим блоком 1-6

Р

НрН этом ((((формационные входы ш-разрядного регистра 1-1 сдвига и первого коммутатор-.(1-2 подключены к информацион-. ному входу у..равпяемой линии задержки 1, выход первого коммутатора 1-2 подключен к информационным входам ð -разрядного регистра 1-4 сдвига и второго коммутатотп ра 1-5, выход ко%рого подключен к информационному выходу управляемой линии задержки 1,, причем управляющий вход управляемой линии задержки 1 подключен к входу второго 1-6 управляющего блока, выход ..(б которого соединен с входом первого управляющего блока 1-3, выход которого.подключен к управляющему выходу управляемой пинии задержки 1, где 1пм (т g)y, I (l - ЦЕЛОЕ ЧИСЛО. рр Временной выравниватепь каналов дпя передачи дискретных сигналов работаетследующим образом, Йискретные последовательности, имеющие временной сдвиг, поступают на вход узла 3, _#_ который производит их синфазирование по тактовой частоте. первый 5 и второй 8 переключатели каналов, оба управляющих бпока 1-3 и 1-6 линии задержки 1 и анали затор 7 наличия выравнивания устанавливаютЯ ся в исходное состояние сигналом "О . С момента начала выравнивания сигнал О" с этих устройств снимается, 8 начале работы выравниватепь даетзадержку дискретной последовательности йер85 ного канала. С выхода первого перекпючатепя 5 дискретная последовательность пер»

Ф вого канала подается нап(-разрядный регистр

-1-1 и коммутатор 1««2 а последовательность второго канала - на первые входы второго

49 переключателя 8 и анализатора 2i

Исходное состояние управляющих блоков

1-3 и 1-6 определяет прохождение диск ретной последовательности первого канЯа через коммутаторы 1-2 и 1-5 на вторые

45 входы переключателя 8 и анализатора 2 без задержки, поатому в .начале выравнивания производится сравнение исходных поспедовательностей, поданных на первый и второй вхоцы выравнивателя. бб B спучае появления временного сдвига между дискретными поспедоватепьностями т определяемого анализатором 2, на его выходе формируется 1 оспедоватепьность, которая

55 проходит через запрещающий блок 6 и переводит управляющий блок 1-6 и одно из (и+Я

° возможных состояний.

По сигапу с упр. впяющего блока 1 6 коммутатор 1-5 коммутирует соответсъЕ т вующие отводы с п-разрядного регистра 14

Э т.е. вносит в дискретную последовательность ч

50 (с)46 первого канала последовательно сдвиг от ну ля «п П,тактов частоты передачи информации.

В случае, если временной сдвиг между дискретными последовательностями первого и второго каналов находится в пределах ц. тактов, то управляюший блок 1-6 остано- . вится в одном из состояний. При этом с регистре 1-4 через коммутатор 1-5 на вторые входы переключателя 8 и внализетора

2 подается дискретная последовательность первого канала, совпадающая с дискретной последовательностью второго канала, нв выходе BHBlIITçàòîðà 2 отсутствуюг импульсы подстройки, в анализатор7 определяет наV личие выравнивания в течение определенного интервала времени, отключает через блок

6 цепь подстройки управляющего блока 3-6 и выдает сигнал на индикатор 4.

При временном сдвиге между дискретными последовательностями более и, тактов анализатор 2 вырабатывает импульс для подстройки, который возвращает блок 1-6 в исходное состояние. При этом блок 1-6 вырабатывает импульс, управляющий блоком рй

1-3, который переводится из исход.юго состояния в первое состояние, @то позволяет подать с выхода коммутатора 1-2 задержанную не (и + 1) тактов последователь« ность первого канала с первого отвода поразрядного регистра 1-1 С выхода коммутатора 1-2 задержанная на (ц + 1) тактов дискретная последовательность первого канала проходит через коммутатор 1-5. нв вторые входы переключателя 8 и енализа- 35 торе 2.

Лри временном сдвиге более и + 1 тактов анализатор 2 продолжает подаватьподстраиваюшие импульсы на вход блока 1-6, последовательно переводя его в одно из 40 ц+ 1 возможных состояний. При этом дискретная последовательность первого кана.ла получает задержку до 2ц + 1 тактов.

Затем, если выравнивание отсутствует, блок

1-6 возвращается в исходное состояние, 4б а блок 1-3 переводится во второе состояние.

В случае, если временной сдвиг между дискретными последовательностями перво

ro и второго каналов находится в пределах п+ п тактов, то анализатор 2 при отсутствии сдвига прекращает вырабатывать импульсы подстройки, в управляющие блоки

1 3 и 1-6 зафиксируют соответствуюшее состояние, при этом анализатор 7 определит наличие выравнивания и отключитцепь подстройки с входа блока 1-6.

Дискретные последовательности соответствуюших каналов отключаются с выходов

:переключателя 8.

Формула изобретения

1. Временной выравнивв тел ь ко í алов для

1 передачи дискретных сигналов, содержащий управляемую линию задержки, ииформацион»" ный выход « горой подключен к анализатору

;отсутстви, выравнивания, фазирую ний узел

:и индикатор, о т л и ч в ю ш и и с я тем, что, с целью упрошеиия сопряжения выравни вателя с аппаратурой для передачи дискрет» ных сигналов, в него введены дополнительный анализатор и два переключателя, выхо» ды узла для феэирования каналов, например

:двух, подключены к входам первого введенного переключателя каналов, первый выход которого подключен к входу анвлизвтораотутствия выравнивания, а второй выход - к информационному4 входу управляемой линии задержки, к управляющему входу которой подключен элемент запрета, входы которого соединены с выходами анализатора отсутствия выравнивания и дополнительного анализатора наличия выравнивания, соединенного с индикатором, причем один из входованелизатора наличия выравнивания подключен к управляющему выходу управляемой линии задержки, в другой — к выходу анализатора отсутствия выравнивания, при этом первый выход первого переключателя каналов допол2 нительно подключен к первому входу второ-!

ro введенного переключателя каналов, к второму входу которого поключен информацион ный выход управляемой линии задержки,управляющий выход которой подключен к третьим входам обоих переключателей каналов.

2, Устройство по п.1, о т л и ч в кш е е с я тем, что управляемая линиязадержки содержит упрввляюшие блоки, коммутаторы, m-разрядный регистр сдвига, с отводами от каждого (ц + 1)-го разряда, подключенными к первому коммутатору,соединенному с первым управляющим блоком,и и-разрядный регистр сдвига с отводами от каждого разряда, подключенными к второму коммутвгору, соединенному с вторым управ«

l ляюшим блоком при этом информационные входыщ-разрядного регистра сдвига и первого коммутатора подключены к информационному входу управляемой линии задержки, выход первого коммутатора подключен к информационным входам и-разрядного регистра сдвига и второго коммутатора, выход которого подключен к информационному sbt

1ходу укрввляемой линии задержки, причем

Г превляюший вход управляемой линии задерж,ки подключен к входу второго упрввляюше1 о блока, выход которого соединен с вхо-. дом первого управляющего блока, выход коэ торого подключен к управляюшему выходу управляемой линии задержки, где%»(4.+ 1) К, :к - целое число.

507 946

Составитель О. Тихонов

Редактор А. Зиньковский Техред Н. Аидрейчук Корректор А, Гусева:

Заказ 146 Тираж 864 Подписное

ЦНИИПИ государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Гагарина, 101