Преобразователь двоичного кода вовременной интервал

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (51) Ч. Кл.- зН ОЗК 13/24 (22) Заявлено 04.02.74 (21) 1993288 26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.03.76. Бюллетень ¹ 12

Дата опубликования описания 20.05.76

Государственный комитет

Совета йсинистров СССР (53) УДК 681.325.53 (088.8) ло делам изобретений и открытий (72) Авторы изобретения

А, M. Коваленко и М. B. Рыжков (71) Заявитель

Ленинградский электротехнический институт связи им, проф. М. А. Бонч-Бруевича (54) ПРЕОБРАЗОВАТЕЛЪ ДВОИЧНОГО КОДА

ВО ВРЕМЕННОЙ ИНТЕРВАЛ

Изобретение относится к области цифровой вычислительной техники и может быть использо вано при создании цифро-аналогoBblx преобразователей.

Из вестные преобразователи двоичного кода во цременной интервал содержат формирователь, преобразователи код — код и IIO следовательного кода в параллельный, а также устройства задержки по числу разрядов преобразователя последовательного кода в параллельный, каждое из которы:< включает в себя устрой ство сдвига.

Цель изобретения — упрощение перестройки при изменении частоты дискретизации, числа уровней гсвантования или порядка кодирования.

Это достигается тем, что преобразователь снабжен по следовательно соединенными задающим генератором и делителем частоты, а каждое устройство задержки — двоичным устройством управления, ключом и элементом «ИЛИ», входы которого подключены к выходам устройства сдвига и ключа, а выход — к одним из входов д воич1ного устройства уп)равления и ключа каждого последующего устройства задержки. Выход элемента

«ИЛИ» последнего устройства задержки соединвн с входом формирователя, другой вход двоичного устройства управления — с выходом соответствующего разряда преобразователя последовательного кода в параллельный, Выходы двоичного устройства улравления устройства задержки подключены к входам ключа и устройства сдв ига, другой вход кото5 рого связан с соответствующим выходом делителя частоты.

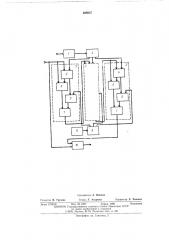

На чертеже представлена функциональная структурная схема устройства.

Оно содержит преобразователь 1 код—

10 .код; преобразователь 2 последовательного кода в параллельный; устройства 3 задержки, включающие в себя двоичные устройства управления 4 и сдвига 5, кл|оч 6 и элемент

«ИЛИ» 7; задающий генератор 8; делитель

15 9 частоты и формирователь 10. формируIQщий сигнал односторонней широтно-импульсной модуляции.

Устройство работает следующим образом.

Принимаемая кодовая последовательность

20 через преобразователь 1 поступает на преобразователь 2, на выходе которого набирается комбинаппя нулей и единиц в соответствии с пр|снятой кодовой группой. Состояние выходов п реобразователя 2 определяет состояние

25 двоичных устройств 4 управления во всех устройствах 3 задержки. Входной им пульс опроса после окончания набора параллельного кода в преооразователе 2 поступает на первое устройство задержки и на один пз

30 входов формирователя 10. На выходе послед508927

10 него формируется передний фронт импульса сигнала односторонней широтно-импульсной модуляции. В первом устройстве задержки входной импульс опроса проходит на один из входов двоичного устройства 4 у правления и на вход ключа 6. В зависимости от состояния двоичного у стройства управления ключ или пропускает, или,не пропускает пришедшей импульс oiIIpoca. Во втором случае, соответспвующем единице, в первом разряде принятой кодо вой комбинации импульс опроса пере бра сы вает двоич|ное устройство управления в другое устойчивое состояние, а изменение состояния устройства управления вызывает изменение со стояния устройства 5 сдвига.

Прямоугольные импульсы с выхода задающего генератора 8 поступают на вход делителя

9 частоты. Число выходов последнего равно числу разрядов преобразуемой кодовой комбинации. На каждом из выходов делителя частоты формируются импульсные нап ряжения, причем частота на каждом последующем выходе в два раза ниже, чем на предыдущем, а частота на первом выходе в два раза ниже частоты задающего генератора 8. Период следования каждой из последовательностей равен времени задержки входного импульса опроса в устройствах задержки.

У стройство 5 сдвига возвращается в исходное colcTosIние пе рвым же импульсом в последовательности с первого выхода делителя 9 частоты. Задержанный импульс подается на элемент «ИЛИ» 7 и далее на вход следующего успройст ва задержки. Та ким образом, входной импульс oIIpoica или проходит через элемент «ИЛИ» 7 без задержки (что соответствует нулю в первом разряде принятой кодовой комбинации) или задерживается на время, равное периоду последовательности импульсов с первого выхода делителя частоты (при записи единицы в первом разряде кодовой комбинации).

Выходной импульс первого успройства задерики поступает,на следующее устройство задержки, где повторяется весь процесс. Та15

25 зо

4О

45 ким образом, проходя все устройства зедержки, входной импульс сдвигается во времени на величину, соответствующую,принятой кодо вой комбинации.

Выход ной импульс последнего устройства заде ржии подается на другой вход формирователя, обеспечивая форми ро вание заднего, подвижного фронта сигнала односторонней широтно-импульсной модуляции. В дальнейшем происходит заполнение преобразователя 2 новой кодовой комбинацией и осуществляется такой же процесс последовательного анализа состоян ий устройств задержки, Ф olp мул а и зоб р ете н и я

Преобразователь двоичного кода во временной интервал, содержащий формирователь, последовательно соединенные преобразователи код в код и последовательного кода в параллельный и устройства задержки по числу разрядо в по следнето, каждое из которых включает в себя устройство сдвига, отл и ч а ю щи и с я тем, что, с целью упрощения перестройки при изменении частоты дискретизации, числа уровней квантования или порядlKB кодирования, он снабжен последовательно соединенными задающим ге нератором и делителем ча стоты, а каждое jjicTlpойство задержки — двоичным устройством управления, ключом и элементом «ИЛИ», входы которо|го подключены к выходам устройства сдвига и ключа, а выход — к одним из входов двоичного устройства у правления и ключа каждого последующего устройства задержки, выход элемента «ИЛИ» последнего устройства задерж ки соединен с входом формирователя, другой вход двоичного устройства упра вления подключен к,выходу соответствующего р азряда п реобразо вателя последовательно го кода в,параллельный, п ри этом выходы, двоичного устройства у правления устройст ва задержании подключевы к входам ключа и устройства сдвига, другой вхо д которого связан с соответствующим выходом делителя частоты.

508927

Составитель А, Изюмов

Техред Г. Андреева

Редактор И. Грузова

Корректор Е. Хмелева

Типография, пр. Сапунова, 2

Заказ 1078/18 Изд. Хз 1227 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5