Датчик кода морзе

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

iii) 50895I

Союз Советских

Саииалистических республик

>

1 (61) Дополнительное к авт. свид-ву (22) Заявлено 06.04.73 (21) 1909147/26-9 с присоединением заявки № (23) Приоритет

Опубликовано 30.03.76. Бюллетень № 12

Государственный комитет

Совета Министров СССР ао делам изобретений и открытий (53) УДК 621.394.61 (088.8) Дата опубликования описания 31.05.7б : 2,Авторы пзобретснпя

В. И, Бал андии, A. А. Семенов и М. И. Катин (71) Заявитель (54) ДАТЧИК КОДА МОРЗЕ единена с соответствующими тактовыми входами буферного накопителя, а другая группа выходов — с блокиратором через интегратор, кроме того один из выходов первой группы

5 соединен с входом блока синхронизации вызова.

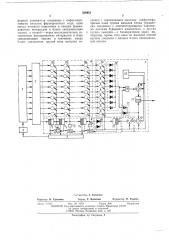

На чертеже приведена функциональная схема датчика кода Морзе.

Датчик кода Морзе содержит последова10 тельно соединенные блок 1 ввода, управляемый вход которого соединен с блокиратором

2, шифратор 3, |буферный накопитель 4 и формирователь 5 кода, один выход которого подключен к входам формирователя б пп15 терминала и блока 7 си нхронизации вызова, а другой — через последовательно соединенные формирователь 6 интервалов и блок 7 синхронизации вызова к тактовому входу блока

8 управления, другой вход которого соединен

20 с управляющим выходом шифратора 3, а также интегратор 9, Одна группа выходов блока 8 управления соединена с соответствующими тактовыми входами буферного накопителя 4, а другая группа выходов — с блокира25 тором 2 через интегратор 9, кроме того один из .выходов первой группы соединен с входом блока 7 синхронизации вызова.

Буферный накопитель 4 содержит и десятиразрядных запоминающих линеек 10п 102, 30 ..., 10„. Блок 8 управления содержит такое

Изобретение относится к телеграфной связи и может использоваться для формирования временных импульсных последовательностей в телеграфном коде Морзе, Известен датчик кода Морзе, содержащий последовательно соединенные блок ввода, управляющий вход которого соединен с блокиратором, шифратор и формирователь кода.

Однако известный датчик кода Морзе имеет низкую точность формирования элементов кода, зависимую от скорости и неравномерности работы манипулятора.

Цель изобретения — повышение точности формирования элементов кода независимо от скорости и неравномерности работы манипулятор а.

Для этого введены буферный накопитель, блок управления, блок синхронизации вызова, формирователь интервалов и интегратор, при этом выходы шифратора через буферный накопитель соединены с информационными входами формирователя кода, один выход которого подключен к входам формирователя интервалов и блока синхронизации вызова, а второй — через последовательно соединенные формирователь интервалов и блок синхронизации вызова к тактовому входу блока управления, другой вход которого соединен с управляющим:выходом шифратора, .причем одна группа выходов блока управления со(51) М. Кла Н 04L 3/04, 13/02

G 08С 19/22

Н 01Н 21/8б, 508951

65 же количество и элементарных блоков управления, состоящих из триггеров 11, 11>, ..., 11„, схем 12ь 122,...,12 совпадения и элементов

131, 13, ..., 13„задержки. Формирователь 5 кода состоит из регистра 14 сдвига, девятивходовой собирательной схемы 15, схемы 16 совпадения, собирательной схемы 17, схем 18 и 19 запрета, тактового генератора 20 и выходного устройства 21, Блок 7 синхронизации вызова состоит из собирательной схемы 22 и триггера 23.

Датчик кода Морзе работает следующим образом, При нажатии одной из клавиш блока 1 ввода по одному из его выходов, соответствующему выбранному знаку, в шифратор 3 поступает сигнал, который распределится ао десяти его выходам в соответствии с промежуточным десятиразрядным кодом. С выходов шифратора 3 код поступает на соответствующие входы буферного накопителя 4 и записывается в запоминающую линейку 10ь ячейки которой в соответствии с кодом записываемого слова переходят в состояние «1».

Одновременно с каждым вводимым знаком в шифратор 3 с его управляющего выхода производится запуск блока 8 управления. При этом триггер 111 срабатывает и выдает сигнал «1» на схему 121 со впадения, на другом входе которой уже имеется сигнал «1» от .последующего триггера 112. Схема 12 совпадения сра батывает и через элемент 131 задержки производит считывание информации с запоминающей линейки 10> буферного накопителя 4 и запись ее в последующую запоминающую линейку 102. Одновременно триггер

11 возвращается в исходное состояние, и выводится из исходного состояния триггер 11>, которыи тем самым обеспечивает совпадение сигналов на следующей схеме 122 совпадения с аналогичным продвижением информации в следующую запоминающую линейку. Такое продвижение информации осуществляется вплоть до записи в последнюю запоминающую линейку 10„с соответствующей работой каждого элементарного блока 8 управления.

Элементы 13ь 13, ..., 13„задержки необходимы для того, чтобы запись информации в запоминающие линейки буферното накопителя

4 произошла раньше, чем поступит на них сигнал считывания от элементарных блоков блока 8 управления. Считывание с последней запоминающей линейки 10 производится по сигналу от триггера 23 блока 7 си нхронизации вызова, которая в свою очередь получает сигнал от формирователя 6 интервалов. Необходимая скорость выхода (формирование) кода из датчика в знаках в минуту в соответствии со средней скоростью ра боты оператора устанавливается регулировкой частоты тактового те нератора 20. При этом благодаря буферной памяти допустимы некоторые отклонения скорости ввода от скорости вывода, вызываемые как неравномерностью кода, так и неравномерностью работы операто5

50 ра на клавиатуре. Блок 7 синхронизации вызо ва исключает совпадение импульсов с последней запоминающей линейки 10„буферного накопителя 4 и импульса считывания от тактового генератора 20, поступающих на регистр 14 сдвига, так как совпадение этих импульсов привело бы к их взаимной компенсации и, следовательно, потере вводимого в регистр 14 сдвига кодового слова.

Таким образом, продвижение информации с одной запоминающей линейки буферного накопителя 4 на другую происходит по мере считывания ее с последней запоминающей линейки 10„по сигналу от блока 7 синхронизации вызова. В случае резкого превышения скорости ввода, т. е. при заполнении всех запоминающих линеек буферного накопителя

4, срабатывает блокиратор 2, управляемый интегратором 9, когда все триггеры 1lь 11,, 11 блока 8 управления выйдут из исходного состояния. При работе датчика тактовый генератор 20 по од ному выходу производит запись «1» в схемы 18, 19 запрета и формирователь 6 интервалов, продвигает в регистре 14 сдвига записанную в нем информацию и приводит триггер 23 через собирательную схему 22 в исходное состояние. С другого выхода тактовый генератор 20 производит считывание записанной «1» со схем 18 и 19 запрета. При считывании со схемы 18 запрета выходное устройство 21 приводится в бестоковое состояние. В случае совпадения сигналов на входах схемы 16 совпадения последняя выдает сигнал, которым запрещается запись «1» в схему 18 запрета, и выходное устройство 21 не приводится в бестоковое состояние, формируя при этом тире. При считывании со схемы 19 запрета сигнал с ее выхода через формирователь 6 интервалов выводит тпиггер 23 из исход ного состояния, который тем самым дает разрешение на запись информации в регистр 14 сдвига с |последней запоминающей линейки 10 буферного накопителя 4 и одHQBipeMeHHQ с записью информации в регистр 14 сдвига приводится через собирательную схему 22 в исходное состояние.

Сигнал с выхода схемы 19 запрета поступает на формирователь 6 интервалов лишь в случае отсутствия информации в регистре 14 сдвига, т. е. при отсутствии сигнала запрета на схему 19 запрета от собирательной схемы

17.

Формула изобретения

Датчик кода Морзе, содержащий последовательно соединенные блок ввода, управляющий вход которого соединен с блокиратором, шифратор и формирователь кода, о т л ич а ю шийся тем, что, с целью повышения точности формирования элементов кода независимо от скорости и неравномерности работы манипулятора, введены буферный:накопитель, блок управления, блок синхронизации вызова, формирователь интервалов и интегратор, при этом выходы шифратора через бу508951 g yl Гг Д !

Составитель А. Кузнецов

Техред T. Колесова

Редактор Н, Суханова

Корректор О. Тюрина

Заказ 1170/1 Изд. № 1279 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2 ферный накопитель соединены с информационными входами формирователя кода, один выход которого подключен к входам формирователя интервалов и блока синхронизации вызова, а второй — через !последовательно соединенные формирователь интервалов и блок синхронизации вызова к тактовому входу блока управления, другой вход которого соединен с управляющим выходом шифратора, причем одна группа выходов блока управления соединена с соответствующими тактовыми входами буферного накопителя, а другая

5 группа выходов — с блокиратором через и|нтегратор, кроме того один из выходов первой группы соединен с входом блока синхронизации вызова.