Арифметико-логическое устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И306РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (") 509870 (61) Дополнительное к авт,. свид-ву(22) Заявлено 22,05.74 (21) 2026035/18-24 с присоединением заявки ¹-(23) Приоритет(43) Опубликовано О5,04.76 Бюллетень ¹» (45) Дата опубликования оиисания 3 08 76

2 (51) M. Кл. G 06K 7/38

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) ygZy68l.327 (088,8) (72) Авторы изобретения

Ф. И. Гринфельд, A. А. Солохин и A. В. Филин

Институт электронных управляющих л ашин (71) Заявитель (54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

1 зобретение относится к области вычис лит льной техники.

Известны арифметико-логические устройства комбинационного типа, содержашие регистры первого и второго операндов, блок распространения переносов и первый логический коммутатор, выходы которого соединены соответственно с выходами первого и второго регистров операндов, первый выход подключен к первому входу блока 1р распространения переносов.

Однако такое устройство не позволяет выполнять операции сдвигов и ряд операций, связанных с обработкой байтов (обмен байтов, расширение знака и т. п.).

Кроме того, в устройстве для каждого разряда имеются два полусумматора, вно сяшие сушественную дополнительную задер ьку в работу устройства при выполнении логических операций, когда сумматор не вы- 20 полняет своих основных функций, а служит только для передачи информации.

Целью изобретения является увеличение быстродействия устройства при выполнении логичес.-:их операций и операций сдвигов и 25 повышение коэффициента использования оборудования.

Г1оставленная цель достигается тем, что в устройство введен блок элементов импликации, блок ключей и второй логиче ский коммутатор, причем второй выход первого логического коммутатора соединен с первым входом блока элементов имплика ции, вторым входол блока распространения переносов и через блок ключей с пер вым входом второго логического комл ута тора, второй вход которого подключен к выходу блока аментов ил|пликаций, второй вход которого соединен с выходом блока распространения переносов.

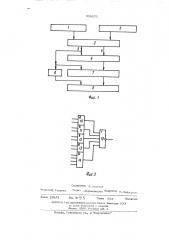

B арифметико-логическом устройстве каждый разряд второго логического коммутатора содержит черыте элемента "И" на два входа, элемент "И" на четыре вхо да, выходы которых подключены соответст венно ко входам элемента "ИЛИ-НЕ".

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — вариант выполнения одного разряда логического кол мутатора.

509870

Устройство содержит элементы 1, 2 первого и второго операндов, логический коммутатор 3 с первым 4 и вторым 5 выходами, блок 6 распространения перено сов, блок 7 элементов импликации, блок 8 5 ключей и логический коммутатор 9.

Один разряд логического коммутатора содержит элементы "И" 10-14, элемент

"ИЛИ НЕ" 15.

Первые входы каждого элемента "И" 10 соединены с первыми входами соответству юших элементов "И" остальных разрядов.

Первые входы коммутатора 9 подключены ко вторым входам элементов "И" 14 дан ного разряда, элементов "И" 10 разрядов на единицу старше. данного, элементов

"И" 11 разрядов на единицу младше данного и элементов "И" 13 разрядов, отличающих» ся от данного на 8 единиц. Первый вход седьмого разряда коммутатора 9 подключен, кроме того, ко вторым входам элементов

"И" 12 разрядов с восьмого по пятнадцатый.

Вторые входы коммутатора 9 подключены к третьим и четвертым входам элементов

И" 14. Выходы всех элементов "И" в каждом разряде подключены ко входам эле мента "ИЛИ-НЕ" 1 5. Выход элемента 1 5 является выходом коммутатора 9.

Устройство работает следующим образом, З

В регистры 1 и 2 помещаются операнды.

Ими могут быть шестнадцатиразрядные слова, байты как B упакованном (два бай та в одном слове), так и в распакованном виде (байт помещен в 8 младших разрядах регистра, а 8 старших разрядов представля ют собой расширенный знак). Прямой и ин версный коды каждого разряда операндов поступают на вход коммутатора 3. и преоб разуются в зависимости от набора управля 40 ющих сигналов так, что в каждом разряде выхода 5 получается одна из 16 возмож» ных логических функций двух переменных, а в каждом разряде выхода 4 конъюнк ция либо прямых значений операндов, ли бо прямого значения первого и инверсного значения второго операндов.

На входы блока 6 распространения пе реносов поступают значения логических функций с выходов 4 и 5 коммутатора 3, 50

На выходах блока 6 образуются значения переносов между разрядами. Значения переносов поступают на входы блока 7 элементов импликации, на другие входы 55 которого поступают значения функций каж дого разряда выхода 5 коммутатора 3.

Блок 7 выполняет для каждого разряда им пликацию значения. функции с выхода блока 6 по значению функции с выхода 5 60 коммутатора 3 и импликацию значения функ ции с выхоца 5 по значению функции с выхода блока 6. Одновременно производится клапанирование значений выходных функций блока 7, прохождение которых разрешается при вы полнении арифметических операций, Ключи блока 8 разрешают прохождение значений функций с выхода 5 коммутатора 3 при вы полнении логических операций и операций сдвигов и запвешают при выполнении ариф метических операций.

В зависимости от набора управляющих сигналов логический коммутатор произво дит следующие преобразования значений входных функций: над значениями функций, поступающих с блока 7 операции конъюнкции с инверси ей в каждом разряде коммутатора 9; над значениями функций, поступающих с выхода блока 8; а) сдвиг влево на один разряд, б) сдвиг вправо на один разряд, в) "нулевой" сдвиг, г) кольцевой сдвиг на 8 разрядов, д) расширение знака, т. е, передачу млад шего байта с "нулевым" сдвигом и заполне ние старшего байта значением разряда младшего байта.

Выполнение этих функций можно проил люстрировать на примере варианта построе ния логического коммутатора 9. Для выпоить» кения конъюнкции с инверсией над значени ями функций, поступающих с выхода блока

7 необходимо, чтобы ключи блока 8 были закрыты, на элементы "И" 14 подавался открывающий сигнал, а на элементы "И

10-13 открывающий сигнал не подавался.

Значения конъюнкций выходных функций блока 7 поступают на элементы "ИЛИ НЕ"

1 5 и затем на выход устройства.

Для выполнения операций над логическими функциями, поступающими с выхода блока

8, необходимо, чтобы выходные элементы блока 7 были закрыты, и на элементы

"И" 1 0 14 подавались управляющие сигна лы.

Рассмотрим выполнение операции сложе ния. В регистр 1 и 2 заносятся слагаемые.

Управляющие сигналы, подаваемые на ло.гический коммутатор 3, настраивают его так, что на каждом разряде выхода 6 обра зуется сумма по модулю 2 входных операн дов, и на выходе 4 — их конъюнкции.

Блок 6 формирует сигнал переносов, по ступающих в блок 7, в, который на вторые входы поступают такде значения функций с выхода 5. На выходе блока 7 для каждого разряда образуются две функции импликации значений входных функций. Ключи

509870 олока 8 запрешают прохождение значений функций с выхода 5 коммутатора 3 на коммутатор 9.

Над функциями с выходов блока 7 в каждом разряде производится конъюнкция и инверсия. Таким образом, на выходе логического коммутатора 9 появляются значения суммы.

Аналогично выполняется операция вычитания. Различие выполнения этих операций 10 в том, что при выполнении вычитания коммутатор 3 формирует: в каждом разряде на выходе 5 функцию эквивалентности входи.- х переменных, на выходе 4 — кон юнкцию значений прямого кода уменьшае- 15 мого и обратного кода вычитаемого, а на блок 6 подается сигнал переноса В нулевой разряд.

Рассмотрим выполнение логических операций. 20

Операция ди.зъюнкции входных чисел выполняется так: в регистры 1 и 2 заносятся обрабатываемые коды, управляюшие сигналы, подаваемые на коммутатор 3, настраивают его так, что на его выходе 5 формируется функция дизъюнкции входных чисел, проходяшая через ключи блока 8 на вход коммутатора 9, управляюшие сигнал. подаваемые на коммутатор 9, настраивают его на передачу с "нулевым" сдвигом, и на выход поступает значение результата операции.

Логический коммутатор 3 может быть настроен управляюшими сигналами на выполнение любой из 16 возможных логических операций, включая передачу отдельных операндов, Независимо от него логический коммутатор 9 может производпть сдвиг результата логической операции на один разряд в обе стороны, кольцевой сдвиг на 8 разрядов (обмен байтов) илп расширение знака, Логический коммутатор 9 может также выполйять отдельные логические операции над двумя байчами одного и того же слова. Например, для получения конъюнкции старшего и младшего байта одного и того же слова на коммутатор 3 подается такая комбинация управляюших-сигналов, чтобы íà его выходе формировался код операнда, а на коммутатор 9 — открываюший управляюший сигнал на элементы "И 13, 14. Коммутатор 9 производит при этом одновременно

"нулевой" сдвиг и кольцевой сдвиг на 8 разрядов. Таким образом, на его выходе образуется в каждом байте конъюнкции старшего и младшего байта.

Также может выполняться в устройстве конъюнкция четырех байтов (одной операцией). Для этого нужно подать на коммутатор

3 такую комбинацию управляюших сигна:юв, чтобы на его выходе 5 в каждом разряде формировалась конъюнкция входных кодов, а на коммутатор 9 - открываюший управляюший сигнал на элементы "И 1 3, 1 4.

При этом на выходе формируется поразрядная конъюнкция четырех байтов.

<формула изобретения

1. Арифметикологическое устройство, содержашее регистры первого и второго операндов, блок распространения переносов и первый логический коммутатор, входы ко» торого соединены соответственно с выходами первого и второго регистров операндов, первый выход подключен к первому входу блока распространения переносов, о т л ич а ю ш е е с .я тем, чт), целью увеличения быстродействия устройства при выполнении логических операций и операций сдвигов и повышения коэффициента псполь зования оборудования, в него введены блок элементов импликации, блок ключей и второй логический коммутатор; причем второй выход первого логического коммутатора соединен с первым входом блока элементов пмпликации, вторым входом блока распространения пе-. реносов и через блок ключей с первым входом второго логического коммутатора, втс» рой вход которого подключен к выходу блока элементов импликацпи, второй вход которого соединен с выходом блока рас;", с.траненпя переносов.

2. Устройство по и. 1, о т л и ч а юш е е с я тем, что каждый разряд второго логического коммутатора содержит четыре элемента "И" на два входа,,элемент "!1" ла четыре входа, выходы которых подключены соответственно ко входам элемента I1, 11 !HE".

509870

Изд. М,4/,.) Заказ 238/3

Тираж 8@4 Подписное

ЦНИ11ПИ Государственного комитета Совета Министров СССР по делам изойретений и открытий

Москва, 113035, Раушская наб., 4

Москва, F нисейская ул., 2 "Гидроводхоз"

Составитель A JEHQB

Редактор Утехина Теаред !.Карандашова Kopperrop М драйв„.