Процессор

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е () Рщ т1

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву2 (22) Заявлено 03.05.73 (21) 1913363/18-24 (51) M. Кл. С 06Ã 15/00 с присоединением заявки №(23) Приоритет(43) Опубликовано05,04.76 Бюллетень № 13 (53) УДК 1 (088.8) (45) Дата опубликования описания 31. 08. 7

Государственный номнтет

Совета Министров СССР по делам изобретений и открытий (72) АвтоРы Р М. Асцатуров, 10. Г. Бостанджян, А. А. Елисеев, А. П. Кондратьев изобретения и Н. А. Мальцев (71) Заявитель (54) ПРОЦЕССОР

Изобретение относится к области вычислительной техники и может быть применено в ЭВМ.

Известны процессоры, содержащие оперативную память, арифметический блок, блок 5 микропрограммного управления, содержащий микропрограммную память, дешифраторы микроодераций управления оперативной памятью и арифметическим блоком, узел форми рования адреса, генератор синхроимпульсов, 1ð узел управления генератором, узел выработки аппаратного гашения и блок электропитания, содержащий узел питания генераторов тока памяти, узел выработки стандартных напряжений, узел управления отключением 15 питания, узел управления включением питания и узел анализа состояния первичной сети.

Недостаток известных процессоров состоит в том, что при отключении электропи 20 тания процессора в случае аварийного состояния первичной сети (отключение одной из фаз первичной сети или недопустимые изменения напряжения) информация, расположенная в оперативной памяти процессора, 25 может быть искажена из-за переходных процессов в узлах ЭВМ, а также из- за того, чтоаварийное отключение питания происходит несинхронно с циклом оперативной памяти, Целью изобретения является повышение надежности процессора.

Для достижения этой цели в процессор введены узел анализа конца цнкла памяти и три элемента задержки. Вход первого эле мента задержки соединен с выходом узла управлейия включением питания, а выход с третьим входом узла питания генераторов тока памяти и со входом второго элемента задержки, выход которого соединен с третьим входом узла выработки аппаратного гашения. Вход третьего элемента задержки

-соединен с выходом узла управления отклю чением питания, а выход с третьим вхо дом узла выработки стандартных напряжений, выход которого соединен с первым входом узла анализа конца цикла памяти, второй, третий и четвертый входы которого соединены соответственно с выходом генератора синхроимпульсов, с выходом

509871 дешифратора микроопераций управления оперативной памятью и с выходом узла анализа состояния первичной сети, а выход соединен с одним из входов узла управления генератором. 5

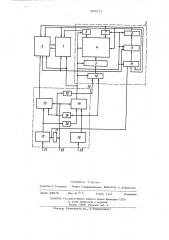

Функциональная схема процессора представлена на чертеже, Процессор содержит арифметический блок 1, оперативную память 2, блок микро» программного управления 3, включающий 10 микропрограммную память 4, узел формирования адреса 5, дешифратор 6 микроопераций управления арифметическим блоком, дешифратор 7 микроопераций управления оперативной памятью, генератор синхроим 10 пульсов 8, узел 9 управления генератором, узел 1 0 выработки аппаратного гашения и узел .11 анализа конца цикла памяти. Про:цессор содержит блок электропитания 12, состоящий из узла 13 питания генераторов 0 тока памяти, узла 14 выработки стандартных напряжений узла 15 управления отключе нием питания, узла 16 управления включением питания, узла 17 анализа состояния первичной сети, первого 18, второго 1 9 и третьего 20 элементов задержки. Процессор содержит также вход отключения пи тания 21, сетевой вход 22 и вход включения питания 23. 30

Устройство работает следующим образом.

Управление работой оперативной памяти

2 осуществляется дешифратором 7, который вырабатывает микрооперации чтения из оперативной памяти 2 или записи в оперативную память 2 в соответствии с микроко мандами, находящимися в микропрограммной памяти 4.

B каждом машинном такте генератор синхроимпульсов 8 вырабатывает серию синхроимпульсов, стробируюших работу в оперативной памяти 2, арифметического блока 1 и микропрограммной памяти 4, При аварийном состоянии первичной се тп узел 17 вырабатывает сигнал о неис- 4б правности, поступающий в узлы 15 и 11.

Еслн фиксация аварийного состояния первичной сети произошла после записи в оперативную память 2, но перед чтением из нее, то в конце текущего машинного такта50 узел 11 выдает сигнал останова генера тора синхроимпульсов 8 в узел 9 управления генератором. Узел 15 при этом формирует сигнал отключения питания генераторов тока оперативной памяти 2, поступающий 55 в узел 13. Через время задержки на элементе задержки 20 формируется сигнал отключения стандартных напряжений, кс торый подается в узел 14. Если фиксация аварийного состояния первичной сети про» 60 исходит при обращении к оперативной памяти 2, т. е. внутри цикла чтения запи» си оперативной i àìÿòè 2, то узел 11 вы дает сигнал останова генератора синхрс импульсов 8 только после того, как полностью отработается,машинный такт, в котором присутствует микрооперация записи в оперативную память 2.

Сигнал включения питания, поступающий в узел 16 приводит к тому, что к первичной сети подключаются узел 14 и 10, По потенциалу гашения происходит сброс в исходное состояние триггерных схем, которые могли бы вызвать непредусмотренное обращение к оперативной памяти

2 в момент подачи питающих напряжений на генераторы тока оперативной памяти 2, После установки потенциала гашения через время задержки на элементе задержки 18 происходит подключение первичной сети к узлу 13 и выдача питающих напряжений на генераторы тока. Продолжительность выра« ботки потенциала гашения определяется суммарным временем задержки элеллентов задержки 18 и 19. По сбросу потенциала гашения узел 5 подготавливает адрес первой микрокоманды микропрограммы гашения, а узел 9 запускает генератор синхроимпульсов 8, после чего начинается выполнение микропрограммы гашения. В результате выполнения микропрограммы гашения сбрасываются в исходное состояние те элементы процессора, которые не сброшены аппаратным гашением, но могут вызвать непредусмотренное обращение к оперативной памяти 2 (а, следовательно, искажение информации в памяти) при работающем генераторе синхроимпульсов 8, Формула изобретения

Процессор, содержащий оперативную память, арифметический блок, блок микропрограммного управления, содержащий мик ропрограммную память, дешифраторы микроопераций управления оперативной памя« тью и арифметическим блоком, узел форми рования адреса, генератор синхроимпульсов, узел управления генератором, узел выработки аппаратного гашения, и блок электропитания, содержащий узел питания генераторов тока памяти, узел выработки стандартных напряжений, узел управления отключением питания, узел управления включением питания, узел анализа состояния первичной сети, причем первый вход узла управления отключением питания соединен со входом отключения питания

509871 процессора, второй вход — с выходом уз ла анализа состояния первичной сети, а выход — с первым входом узла питания генераторов тока памяти, второй вход кото рого соединен с первым входом узла выработки стандартных напряжений, со входом узла анализа состояния первичной сети и с сетевым входом процессора, а выход соединен с первым входом оперативной памяти, второй вход которой соединен с первыми !0 входами арифметического блока, узла управления генератором, узла формирования адреса и с выходом узла выработки аппаратного гашения, первый вход которого соединен с первыми входами дешифраторов микроопера- 15 ций управления оперативной памятью и арифметическим блоком, генератора синхроимпульсов, микропрограммной памяти, со вторыми входами арифметического блока, узла формирования адреса, узла управления 20 генератором, с третьим входом оперативной пал яти и с выходом узла выработки стандартных напряжений, второй вход которого соединен со вторым входом узла выработки аппаратного гашения и с выходом узла уп- 25 равления включением питания, вход которого соединен со входом включения питания процессора, второй вход микропрограммной памяти соединен. с выходом узла формирования адреса, первый выход соединен со вторым 30 входом дешифратора микроопераций управления арифметическим блоком, выход которого соединен с третьим входом арифметического блока, выход генератора синхроимпульсов соединен с четвертыми входами оперативной памяти и арифметического блока, с третьим входом микропрограммной памяти, второй выход которой соединен со вторым входом дешифратора микроопераций управления оперативной памятью, выход которого соеди нен с пятым входол1 оперативной памяти, выход которой соединен с пятым входом арифметического блока, выход которого со единен с шестым входом оперативной памяти, отличаюшийся тем,что,сцелью повышения надежности процессора, он дополнительно содержит узел анализа конца цикла памяти и три элемента задержки> причем вход первого элемента задержки со единен с выходом узла управления включе нием питания, а выход - с третьим входом узла питания генераторОв тока памяти и со входом второго элемента задержки, вы ход которого соединен с третьим входом узла выработки аппаратного гашения; вход третьего элемента задержки соединен с выходом узла управления отключением питания, а выход - с третьим входом узла выработки стандартных напряжений, выход которого соединен с первым входом узла анализа конца цикла памяти, второй, третий, и четвертый входы которого соединены соответственно с выходом генератора синх роимпульсов, с выходом деыифратора микроопераций управления оперативной памятью и с выходом узла анализа состояния первичной сети, а выход соединен с третьим входом узла у-правления генератором.

50987 1

Составитель Т.Лрсшев

Редактор Л. Утехина Текред И.Карандашова корректор Х.Лейзерман

Заказ 238/4 Изд. K 3 5 Тираж 884 Подлисное

ЦНИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

Москва, ll3035, Раушская наб., 4 москва, Енисейская ул., 2 "Гипроводхоз"