Регистр сдвига

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 5Î9891 (61) Дополнительное к авт. свид-ву (22) Заявлено02.12.72 (21) 1856285/18-24 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано05 04 76, Бюллетень ¹ 1 (45) Дата опубликования описания05.07.76

2 (51) М. Кл. (11С 19/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК681.827.088 (088.8) (72) Авторы изобретения

Т. В. Донецкая и Г. ф. Рыбакова (71) 3аявитель Ленинградский ордена Ленина политехнический институт им. М. И. Калинина (54) РЕГИСТР СДВИГА

Изобретение этносится к области вычислительной техники и может быть использовано при создании устройства для выполнения наименьшей пачки импульсов из анализируемой серии пачек, цля счета и запэми- 5 нания числа импульсов в ней.

Известен регистр сдвига, сэдержашнй в каждом разряде триггер, выход которого через лемент задержки подключен к первому р входу триггера последующего разряда. Вхсды младшего триггера регистра подключены к шине входного сигнала и шине сброса непосре;ственнэ, а вторы входы остальных триггеров подсоедины к этим же шинам 15 через элементы "ИЛИ". Регистр сдвига считает в унитарном коде число импульсов в пачке, поступаюшей по шине входного сигнала и помнит его лишь до момента прихода по шине сброса импульса, предшествуюшегэ 20 следуюшей пачке.

Однако функциональные возможности такого регистра ограничены. целью изобретения является возможность 5 запоминания числа импульсов в наименьшеи пачке из поступаюшей серии пачек, Зта цель достигается тем, что предложенный регистр содержит блок разрешения сдвига, блок разрешения сброса, триггер начального сравнения и элемент "ИЛИ" на первом входе триггера младшего разряда, шину установки в начальное состояние, подключенную к первым входам элементов "ИЛИ и к первому входу триггера начального сравнения; причем один выход блока разрешения сдвига соединен со входом триггера младшего разряда, остальные выходы — со вторыми входами элементов "ИЛИ"; управляюшие входы блока разрешения сдвига соединены с выходами всех триггеров, кроме младшего разряда регистра, и с выходом триггера начального сравнения; основной вход блока разрешения сдвига подключен к шине входного сигнала, один выход блока разрешения сброса соединен со входом триггера начального сравнения, остальные — соответственно с третьими входами элементов "ИЛИ"; управляюшие входы блока разрешения сброса соединены с выходами всех

509891 триггеров регистра; основной вход блока разрешения сброса соединен с шиной сброса.

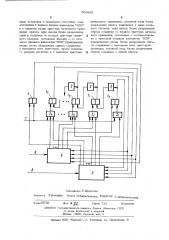

Блок-схема регистра представлена на чертеже. 5

Регистр состоит из триггеров 1 в каждом разряда, элементов задержки 2, элементов ИЛИ 3, триггера начального сравнения 4, блока разрешения сброса 5, блока разоешения сдвига 6, шины установки в íà- l0 чальное состояние 7, шины сброса 8 и шины входного сигнала 9.

Шина 7 соединена с первым входом триггера 4 и через элементы "ИЛИ" 3 с первым входом триггера 1 младшего разряда 15 и вторыми входами триггеров 1 остальных разрядов регистра. Шина 8 через блок разрешения сброса 5 соединена со вторым вхс дом триггера 4 и дополнительно через элементы "ИЛИ" 3 с первым входом триггера 20

1 младшего разряда и вторыми входами триггеров 1 остальных разрядов регистра.

Шина 9 через блок разрешения сдвига 6 соединена со вторым входом триггера 1 младшего разряда и дополнительно через 25 элементы "ИЛИ" со вторыми входами триггеров 1 остальных разрядов регистра.

Выходы всех триггеров 1 соединены сг входами блока разрешения сброса 5, который выполнен таким образом, что разреша- З0 ет сброс триггеров в состояние «О" лишь в части регистра с весами, большими чем, вес младшей единицы, записанной ь данный момент в регистре. Выходы всех триггеров l. кроме младшего, и выход триггера 4 35 соединены со входом блока разрешения сдвига 6, который выполнен таким образом, что разр шает сдвиг "единицы" лишь в части регистра с весами, меньшими, чем вес старшей единицы, записанной в регистре 40 перед началом анализа текущей пачки. Число триггеров 1 должно быть хотя бы на единицу больше, чем число импульсов в минимальной пачке.

Регистр сдвига работает следующим об- 45 разом.

Перед началом работы по шине 7 подается импульс, который устанавливает в состояние "1 " триггер 1 младшего разряда и триггер 4 и в состояние "0" все осталь- 50

rrbre триггеры регистра. После этого по шине 9 подаются импульсы анализируемых пачек, отделенных друг от друга импуль— сами сброса, подаваемыми по шине 8. Импульсы, приходящие по шине 9, сдвигают

"1" из тригverra млацшего разряда регистра в сторону старших разрядов. Число импульсов в первой пачке может быть большим, равным или меньшим, чем число триггеров 1 в регистре сдвига. В первом и втс - 60 ром случае число сдвигов единицы таково, что после окончания анализируемой пачки импульсов все триггеры 1 оказываются в состоянии "0", триггер 4. — в положении

"1", а после импульса сброса триггер 4 и триггер 1 младшего разряда — в состоянии "1", остальные триггеры 1 — в состоянии "0", т.е. схема возвращается в начальное состояние. В третьем случае импульсы первой исследуемой пачки сдвигают

"1" из триггера 1 младшего разрядa лишь в L + 1=й разряд (где L — число им1 1 пульсов в этой пачке) По окончании пачки в состоЯнии "1" оказываются триггер 4 и триггер 1 +1-го разряда, а после импуль1 са сброса — триггер + 1-го разряда

1 и триггер младшего разряда, все остальные триггеры — в состоянии "0".

Число импульсов L < в следующей пачке может быть большим, равным или меньшим, чем L . Если L< L (как в рассмотренном выше случае), когда число импульсов первой пачки больше или равно числу триггеров 1 регистра), то состояние схемы в результате анализа этой пачки не изменяется, т.е. к приходу очередной пачки в состоянии "1 " вновь оказываются триггер + 1-го разряда и младший триггер

1 регистра. Если же 1 (, то после

2 окончания пачки в состоянии "j оказывают2

"я триггеры L1 + 1-ro L + 1-го разрядов,. а после прихода импульса сброса триггер r + 1-го разряда и младший триг2 гер, остальные триггеры — в состоянии "0". ! аким образом, после анализа каждои из поступающих на шину входн« о сигнала пачек импульсов запомненная в регистре "1 " или остается на месте или и ремещается в сторону младших разрядов регистра. После анализа всей серии пачек "1 " остается в триггере L -го разряда r + 1, который

min соответствует числу импульсов L в наПЫП имен ьrrreA пачке. формула изобретения

Регистр сцвига, содержащий в каждом разряде триггер, выход которого через элемент задержки подключен к первому входу триггера последующего разряда, второй вход которого подключен к выходу элемента "ИЛИ" шину сброса и шину входного сиг нала, отличающийся тем, что, с делью запоминания количества импульсов в наименьшей пачке из серии поступающих на вход пачек, в него введен блок разрешения сдвига, блок разрешения сброса, триггер начального сравнения, элемент иЛИ" на первом входе триггера младшего разряда и

509891

Составитель Р.Яворская

Редактор Л Утехина Техвед И.Карандашова корректор г д б

Заказ 5538

Изд. K Тираж 723

Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 шина установки в начальное состояние, подключенная к первым входам элементов "ИЛИ" и к первому входу триггера начального сравнения: причем один выход блока разрешения сдвига соединен со входом триггера млад- 5 щего разряда, остальные выходы - со втс рыми входами элементов "ИЛИ" управляющие входы блока разрешения сдвига соединены с выходами всех триггеров, кроме младшего разряда регистра и с выходом триггера 10 начального сравнения; основной вход блока разрешения сдвига подключен к шине входного сигнала; один выход блока разрешения сброса соединен со входом триггера началь ного сравнения, остальные — соответствен» но с третьими входами элементов "ИЛИ", управляющие входы блока разрешения сброса соединены с выходами всех триггеров регистра; основной вход блока разрешения сброса соединен с шиной сброса.