Делитель частоты с переменным коэф-фициентом деления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Соавтскнх

Социалистических

Республик

К АВТОРСКОМУ СВИДИИЙЬСУВУ (61) Дополнительное к авт. свид-ву (22) Заявлено27 08.74 (2!) 2057219/21 с присоединением заявки № (23) Приоритет

Ю (5}) М. Кл. Н ОЗК 23/00

Государственна}й наинтат

Совета Ннннстрав СССР ао делам нзобретаннв н откр}нтнй (43) О}тубликоваиа05.04.76. Бтоллетень,пй} 1З (45) Дата опубликования рписания }2- Ов " ($3) УДК 621.374..4 (ОЕВ,Е) (72) Автор:. изобретения

И. С, Конькин (71) 3

Заявитель Сарапульский ордена Ленина и ордена Т!>удовогс К!>1!О}1с>-О 3}}Яме!1у рад}}озяВОД ИМ. О}>джоннкид:!е (54 ) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕН НЫ!М К< }ЗФ >И Л !1,! ЕН 1 i; >Л - ДЕЛЕНИЯ!

110}! ис:}т:ч;>}>к:- » ;-О,!Пс! 1-» Г:i я>;.-.:}врач !!Ос1!едовятель:! c::ci;.II;-;- i,.> е и!1Вертор и элемент И>-1-1!., О.;. и ил В}-,О>1 >B;.:.ементов

И-НЕ BTi>pOII C >"-: м,! !>I> }!CII;1! i! l IO!I KJ!IO }9 }IE I

К ИЛЕ!!>,!Е ИСТОЧ1!И}:.ч ВВ?;,>;ii:, >ГО СИI }!ЯЛЯ ЧЕ-е

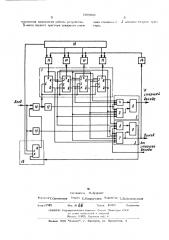

ДЕЛИТЕЛЬ ЧЯСТОТЫ СОДЕРЖИТ д! КЯДНый счетчик 1, схемы фиксации 2 и 3, В кяжду}О из которь!х соответственно Входят элементы И -НЕ 4, 5 и 6, 7 и триггер

8, 9, злементы И--НЕ 10 и 11, иивертсИзобретение относится к: импульсной технике и может быть использовано В различных радиотехнических устройствах, В том числе в цифровых синтезаторах частоты. 5

Известен делитель частоты с пере ме н1HbI}>j коэффициентом деления, содержаший декадный счетчик,. вход которого соединен с выходом элемента И-НЕ, один вход которого подключен к клем} е источника вход- !О ного сигнала, а другой вход — к выходу коммутируюшего триггера, и две схемы фиксации.

Недостатками известного делителя час-.оты являются сложность и ненадежность работы вследствие паразитного Влияния состояний первого и четвертого триггеров декадного счетчика во время установки исходного состояния.

B предложенном делчтеле частоты указанные недостатки устранены благодаря тому, что каждая схема фиксации выполнена на двух элементах И-HE и триггере, причем одни из входов элементов И-HE п первой схемы фиксации соединены с клемпез инвертср, д>,;"i ие >!. -:,;,,; Всех злемен1 тОВ И-!31:, схем >>>1 .кса ii!!i >;!Кл!Очепы к

ВЫХОЛЯМ ДЕКЯЛ!ИЛ-> С, !И::,-Я, }}1>КОДЫ ЭЛЕ

F ме}IтoB I i iÃ> ка>кд .>!1 !.,Ке"..". ü ф>:ксацн11 под«

КЛЮЧЕНВ! К УСТЯ!}ОВОЧ! 1.>М ВХОДЯМ СООТВЕТ« ствук>!1!е! О триггера. Б}:!код тригге}>я, Вхо дяи}ВГ О Bo В тo I> Yjo .Ке му Й}к1: >11}ни с Оеди> нен с упрявля}ol!I!ì Входом ком}!утиру}сшеГО тр1>> Гера, Я В}(сд пе!>1>ОГО триГГеря

ДЕКЯД}}О((> С ЧЕТИ ИКЯ СОЕЛ!}ИЕ» С «ВХОДОМ, Второго триггеря.

НЯ чертеже предстЯВПВИЯ структурная . схема предложенного делителя частоты с переме}1ны},: коэффициентом деления.

50! 999 ры 12, 13, 14, коммутируюший триггер

15 и кодируюшее устройство 16, Работает делитель частоты q установившемся режиме при коэффициенте деления первой декады ЙФ 0 следующим обра зом, В исходном состоянии в декадный счет чик 1 с естественным порядком счета записано число ю" 10- -Й + 1. Коммутирующий триггер 15 находится в нулевом со- 16 стоянии. На К-входе триггера кодирующим устройством 16 поддерживается по> стоянный высокий уровень . Триггер 8 находится в единичном состоянии, триггер

9-в нулевом.

И

Первый входной импульс не проходит на С-вход декадного счетчика 1, но переводит в единичное состояние коммутирующий триггер 15. Второй и последующие входные импульсы проходят через эле- мент И-HE 10 и попадают на С-вход декад ного счетчика 1.

В первом неполном цикле счета до нуля (Й фОу 1) состояние триггера 8 не изменяется. В первом состоянии первого полного цикла счета от единицы до нуля на выходе элемента И HE 5 устанавливается низкий уровень и триггер 8 пере.одит в нулевое состояние.

ЗО

В шестом аостоянии декадного счетчи. ка 1 на выходе элемента И-HE 4 устанавливается низкий уровень, игтриггер 8 возвращается в единичное состояние, В последующих циклах счета состояния элементов И-НЕ 4 и 5 повторяются и триггер 8 формирует импульсы переноса со скважностью два. Инвертор 12, имея время задержки выключения не меньшее, чем время задержки переключения любого триггера декадного счетчика, исключает влияние состояния триггеров во время очета, Когда старшие декады счетчика заполняются полностью, на соответствуюшем входе элементов И НЕ g и 7 возникает :, высокий уровень, а декадный счетчик 1 продолжает последний цикл счета. B де-. вятом состоянии счетчика импульс с выхода инвертора 13 появляется на выходе 5п элемента И-НЕ 6 в виде коротного низкого уровня и устанавливает триггер 9

t в единичное состояние, разрешающее" подготовку коммутирующего триггера 15 для переключения в нулевое состояние. 55

В десятом состоянии декадного счетчика на выходе элемента И-НЕ 7 в >никает короткий низкий уровень и триггер 9 возвращается в нулевое состояние. В это же время коммутируюший триггер 15 пере- щ ключается по С-входу в нулевое состояние и загшрает вход элемента И-НЕ 10.

Короткий низкий уровень на выходе элемента И-НЕ 7, являющийся выходным, импульсом делителя, -инвертируется инвертором 14 и поступает на вход элементов

И-НЕ 11. В соответствии с кодовой комбинацией, поступаюшей с выходов кодирую. щего устройства 16, на выходе элементов И-НЕ 11 врзникйет короткий низкий уровень, который, воздействуя на. 3;вход триггеров, устаневливает декадный счетчик

1 в исходное состояние, В режиме работы делителя с коэффициентом деления первой декады N †. 0 постоянный низкий уровень, поступающий с коди, руюшего устройства 16 на К-вход коммутирующего триггера 15, удерживает его в единичном состоянии. В декадный счг Tчик 1 при установке исходного состояния ничего не записывается.

Связь между Я -входом первого триггера и J -входом второго триггера декадного счетчика исключает паразитное влияние состояния первого и четверто — î тоиг.гeð» во время установки исходного. состояния, в частности при записи кодовой комбинации 1001.

Формула изобретения

1. Делитель частоты с переменным коэффициентом деления, содержащий декадный счетчик, вход которого соединен с выходом элемента И-НЕ, первый вход которого подключен к клемме источника входного сигнала, а второй вход — к выходу коммутируюшего триггера, и две схемы фиксации, отличающийся тем, что, с целью упрощения устройства, каждая схема фиксации выполнена нв двух элементах И-НЕ и триггере, причем одни из входов элементов И-НЕ первой схемы фиксации соединены с клеммой источника входного сигнала через последовательно соединенные инвертор и элемент И-НЕ, один из входов элементОв И-HE второй схемы фиксации подключенг; к клемме источника входного сигнала через инвертор, другие входы всех элементов И-НЕ схем фиксации подключены к выходам декадного e K ; выходы элементов И-НЕ каждой схемы фиксации подключены к установочным входам соответствующего триггера, выход одного из которых, входящего во ч вторую схему фиксация, соединен с управляюшим входом коммутирующего триггера, 2. Делитель частоты по и, 1, о т— л и ч а ю ш и Й с я тем,.что, с целью

Г>

J «Входогл втОРОГО тРн1

Составнтель М,Аудрннг

Техред E.Подуругггина орректор 1. Побровольская

Редак гору.орловская г

Изд, М gg Тираж 1020 Подггисное

Ш1ИИггИ Государственного комитета Сои та Мииистрои СССР

i1o дедам изобретений и открытий

Москва, l l3035, Раун)скак ггаб., 4

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4 повы1иения надежности работы устройства, Ь -вход первого триггера декадного счеъчика соедине г с гера. арф ей аде иИй

bl