Устройство для деления частотыповторения импульсов

Иллюстрации

Показать всеРеферат

( эт еи (l

О Il И C А Н И Е <1> д11>г((11

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Реслублик (61) Дополнительное к авт. саид-ву (22) ЗаявленоО 1.11.74 (2j) 2072900/26-21 с присоединением заявки № (03) Приоритет (4;1) Опубликовано(1.>.04.7(>. Бюллетень М 13

2 (51) М. Хл.Н 03К 23/00

Гаоударотаеииый коиитет

Совета Ииииотроа СССР оо делви иообретеиий и открытий (5 3) УДК621 374..4 (088.8) (45) Дата опубликования описания () <.>„71;

O (?2) Автор изобретения

В. П. Савин (?1) Заявите. ь ()4) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ ПОВТОРЕНИЯ

ИМПУЛЬСОВ

Изобретение относится к код>1рованию и преобразованию информации.

Известно устройство для деления частоты повторения импульсов; содержащее последовательно соединенные элемент запрета, делитель частоты и сумматор, выход которого соединен с уп(>яв><як>г>1им входом элемента запрета, Цель изобретения — обеспеченис-: точного процесса деления частоты Irol Top<=ния 10 импульсов нР» коэффициенты деления, представленные неправильной дробью.

В предлагаемое устройство введены коммутатор, один из управляк>ших входов к(.торог0 соединен с выходом д(лителя чяс Iî- И ты, другой - с выходом сумматора, входы которого соединены с выходами коммутатора, и блоки памяти кодов числителя и знаменателя, выходы которых полк>>к>чены . ко входам ко ммута тора, 20

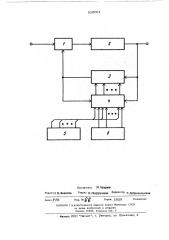

На чертеже представлена структурная схема устройства, B устройство для деления частоты пс вторени я и мпульсов входят зле мент з я прета 1, делитель частоты 2, сумматор накал- Ж, лнваюшего типа 3, коммутатор 4 с числом направлений, рави(>1м колнч(ству ря lpsIJIOI)

K0JIB знаменателя др(>бно1 0 коэффициента деления, бл01; памяти кода числит(ля дроб« ной части коэффици< нтя де>1ення .>, блок памяти KOI JIJ> 0>llçì(íßT<)JIß пробно>1 чясти

КОЭ<1>фици<>НТЯ ДЕЛЕНИЯ 6.

Работает устрой(.тво слгдуюшим образомм.

Импульсы <- ???????????????? ????????????????????, ??>одлежянн и делению, поляк>т; я ня элг мент зяп(>ет<1 1 и дя;1<>е, в (лучг>о ог(тствия зяпре1г> с <)уммато(»(3, и >ступают на деJIlI I(л1 ч>и Т<>ч l,l 2.

><.<>ждь<й икн>ульс с д лиг ля час roгы 2

B качестве сигняля у>13><<В<1(>ния 110 тупя<>т ня сумм<11.>>> 3 и на yIq>;>e>1>I>0>;I>I>i вход коммутатора 4. Нри этик> кок>;,>утяг<>р 4 подклк>чает K(> Вход>>м (: ммят<>ря 3 Выхо ды блока нямятн 5, сумма>ор <:кл:>д>»вяет няходяшнйся H нем ос:таток >т пр- л >пушего сложения с кодом числителя блока памяти 5.

Если сук<матор п>реполнен, на (гo выходе формируется сигнал управления, К0оооо торыя поступает на вход управления элементе запрета 1 и переводит делитель частоты 2 нз режима деления в режим хра» ненни.

Сигнал управления йоступает также на. второй управлявший вход коммутатора 4.:

При этом коммутатор подклкяает ко вхо» дам сумматора 3 входы блока памяти 6, и сумматор складывает код знаменателй C

«Ю остатком от предыдущего сложения. лагодаря этому apeapamaxecs переполнение сумматора и запрет элемента запрета 1, Средняя частота н вьйдоде устройстна:

1 .Ф,1

53 » В

Ф И Р+ где f - частота повторении нмцульсо@ подлежащая делению

И - заданный дробный козффищнент деления час иуРы

Р двоичное число целой части .И р 4 щ - двоичное число числитела Фробной

- MOT8 Й".; ъ - двоичное число знаменателя дро5. ной чести Й .

Коэффициент деления делителя частоть

2 устанавливается равный числу Р, в

J блок памяти 5 записывается число 63 а s блок памяти 6 - дополнительный код числа Ft . Число разрядов блока памяти5 устанавливается равным числу разрядов блока памяти 6. Число разрядов блока па-.

5 мяти 6 определяется только количеством разрядов числа @, что значительно упрощает устройство.

Формула изобретения

В

Устройстао для деления частоты поить ренин импульсов, содерматее нос ладов = -, теано соеднненйные элемент -запрета, де ; . дизель частетй н сумматор, аьаод «ото

Р раз .о .соедийен с уйравдакииим вяодом епе меюа запрета, . о т л и ч е в щ е е-е а . тем, что, с целью,ебесйеченин точнси о процесса деления частоты повторения им йульсов si.нонффициенты деления, пред- . ставленные неправильной дробью, в него виедены коммутатор, одий из управляющих

- входон которого соединен с выходом де лителя частоты, другой - с выходом сум.: матора. входы которого соединени .с вы® ходаМи Коммутатора, и блоки памяти кодов числителя и знаменателя, выходы которых подклкяены ко входам коммутатора.

Заказ, ЯМ

Изд. М 1 ирак 1029

Подписное

11НИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Филиал ППП Патент „r Ужгород, ул. Проектная, 4

Составитель М.А яфИИГГ

Редактор B.Ôåäîòîù техред р По зудцща корректор т. д< ъ