Устройство для сравнения следующих друг за другом чисел

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 1)!) 5107И

ИЗОБР ЕТЕ Н И Я

К АВТОРСКОМУ СВМДЕТЕЙЬ СТВО

Со)оз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 05,05.74 (21) 2021902, 24 (51) М. Кл. 6 06F 7/04 с присоединением заявки №

Совета Министров СССР ао делам изобретений н открытий (53) УДК 681.325(088,8) Опубликовано 15.04.76. Бюллетень ¹ 14

Дата опубликования описания 25.05.76 (72) Автор изобретения

А. А. Козлов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ СЛЕДУ)«ОЩ)1Х

ДРУГ ЗА ДРУГОМ ЧИСЕЛ

Государственный комитет (23) Приоритет

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации.

Известно устройство для сразпения следуioщих друГ за друГОМ чисел, содерж2)цее «ходной регистр, информационный вход которого подключен к первой входной шине, а информационные Выходы соединены с соответствующими входами коммутатора, выходы которого подключены ко входам выходного регистра, элементы «И» и «ИЛИ».

Целью изобретения являет я расширение класса решаемых задач. B описываемом уcIройстве это достигается тем, что в него Введены дешифратор, счетчик, два блока параметрического сравнения и два сумматора, первые входы которых объединены и подключены к выходному реп)стру, а вторые входы полк;почепы ко второй и третьей Входным шипам, первые входы обоих блоков параметрического сравнения объединены между собой и подключены ко входному регистру, а вторые входы подключены к выходам сумматоров, выходы блоков параметрического сравнения соединены со входами первого элемента «И», выход которого подключен к первому входу второго элемента «И», второй вход которого соединен с четвертой входной шиной, а выход подключен к первому входу элемента «ИЛИ», второй вход которого подключен к пятой входной шине и информационному входу счетчика, 2 выход — к управляющему входу входного регистра, выход последнего разряда которого

))Од! .,почсil к Ilcpi)0 «!«Вход) TpñòüeÃO э,)емспта «И», и вход первого разряда соединен с Вы "Одо)! тр«".тьсГО э !с)!сп" - <

«ХОД I

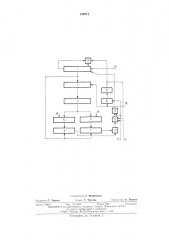

На ч! р Гсжс );р))«с, 1сн «1 сх;з! с! тс1!)OiicT«a.

Опа состо.IT !Ia «ходпого рсг));тр«! 1, !«Ох)х! «)5 ГIITopa ., ВыхОдl)ОГО;:".!ч)стр

-1 )! 5, б, )Око« II ii! I;i)leò!) п«)с« !, )ГО cp « «lie!1 IIH 6

7. счет«)п! .2 Ь, д« lilliippс)тОра 9, .10! ))-!eel«II#

;кем «)1» О, 11 ): )2, схс))ы «1)Л11» 13 и

);хо:!пых .и!i! )-i — 19.

В исходцох! рс.-);стрс 3 счстчпк 8 находится

«пулевом состоянии, и схемы «И» 10 и 11 закрыты потсн,llалом с деIIIII«$)paтора 9. Прп этом код числа. пост па)ощп)! со «ходноп шп16, IIOCpC707 «0)i Ta .TO«! !X iI)lii«,,il>COB.

)) ступающих с ill!: )ы 17 через схсз) «11Л11» 13, заполняет Вхо !пoii регистр. Одновременно

Т I«T C) «bl e I! З П «7Л Ь С Ы П 0 С Г« П «а )О Т Н 2 «Х 0 Д С Ч ET«»I!ca 8. С«)стчпк перс«0,7нястс!!, i.огда i O.l чп«..ла заполl«aåò Вхо.,пой регистр. Прп этом по:30 тспцпалом с:-ыхода лсшпфратора 9 открыва5l07ll

10 ется схема «И» 10, и входной регистр переключается на работу по рекурентному циклу; кроме того, разрешающий потенциал поступает на схему «И» 11. Код числа, находящегося в регистре 1, поступает на коммутатор 2 и первые входы блоков парамегрического сравнения 6 и 7. Код числа, находящегося в регистре 3, поступает на первые входы сумматоров 4 и 5. На вторые входы сумматора 4 с шины 18 поступает прямой код числа, на которое должны отличаться числа, находящиеся в регистрах 1 и 3, а на вторые входы сумматора 5 с шины 19 поступает дополнительный код этого числа.

Таким образом, на выходе сумматора 4 будет код суммы, а на выходе сумматора 5— код разности числа, находящегося в регистре 3, и числа, поступающего на вторые входы этих сумматоров.

Блок параметрического сравнения 6 производит сравнение числа, находящегося в регистре 1, с числом, поступающим с сумматора 4, и разрешающий потенциал на его выходе будет только в том случае, если число, находящееся в регистре 1, меньше числа, поступающего с сумматора 4. Блок параметрического сравнения 7 производит сравнение числа, поступающего с сумматора 5, с числом, находящимся в регистре 1, и разрешающий потенциал на его выходе будет только в том случае, если число, находящееся в регистре 1, будет больше числа, поступающего с сумматора 5.

Таким образом, если число, находящееся в регистре 1, отличается от числа, находящегося в регистре 3, на величину, меньшую чем число, поступающее на вторые входы сумматоров, то схема «И» 12 будет открыта, и разрешающий потенциал с нее поступит на схему «И»

11. При этом импульсы частоты перестройки, превышающей тактовую частоту на величину, достаточную для завершения рекурентного цикла регистра 1, поступают с шины 14 через открытую схему «И» 11 в тактовую цепь регистра 1.

Регистр 1 перестраивается по рекурентному циклу до тех пор, пока находящееся в нем число не будет отличаться от числа, находящегося в регистре 3, на величину, не меньшую заданной числом, поступающим на вторые входы сумматоров. Как только это произой15

50 дет, схема «И» 12 будет закрыта по одному из входов и закроет схему «И» 11. При этом импульсы частоты перестройки в тактовую цепь регистр а 1 не пройдут.

По окончании цикла работы, импульсом, поступающим с шины 15, счетчик 8 будет сброшен в нулевое состояние, а содержимое регистра 1 через коммутатор 2 перепишется в регистр 3, после чего устройство готово к следующему циклу работы.

Формула изобретения

Устройство для сравнения следующих друг за другом чисел, содержащее входной регистр, информационный вход которого подключен к первой входной шине, а информационные выходы соединены с соответствующими входами коммутатора, выходы которого подключены к входам выходного регистра, элементы «И» и

«ИЛИ», отл и ч а ю ще ес я тем, что, с целью расширения класса решаемых задач, в него введены дешифратор, счетчик, два блока параметрического сравнения и два сумматора, первые входы которых объединены и подключены к выходному регистру, а вторые входы подключены ко второй и третьей входным шинам, первые входы обоих блоков параметрического сравнения объединены между собой и подключены ко входному регистру, а вторые входы подключены к выходам сумматоров, выходы блоков параметрического сравнения соединены со входами первого элемента «И», выход которого подключен к первому входу второго элемента «И», второй вход которого соединен с четвертой входной шиной, а выход подключен к первому входу элемента «ИЛИ», второй вход которого подключен к пятой входной шине и инфор мационному входу счетчика, а выход — к управляющему входу входного регистра, выход последнего разряда которого подключен к первому входу третьего элемента «И», а вход первого разряда соединен с выходом третьего элемента «И», второй вход которого подключен к третьему входу второго элемента «И» и выходу дешифратора, вход которого соединен с выходом счетчика, управляющий вход которого соединен с управляющим входом коммутатора и с шестой входной шиной.

5I0711

Составптечь P. Яворовская

Текрел T. Трусова

1,орректор О. Тюрина

Редактор Л. Тюрина

Типография, пр. Сапунова, 2

Заказ 108/3 Изл. X- 1264 Тираж 864 110;111IICllOC

ЦНИИПИ Государственного козгитета Совета Министров СССР по делаги изобретений и открытий

113035, Москва, Ж-35, Раугиская наб., л. 4!5