Параллельный сумматор

Иллюстрации

Показать всеРеферат

0 П И С А -М "и"eMЗОБРЕТЕ8И% р) .ИО713

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 14.06.73 (21) 1932236/24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.04.76. Бюллетень ¹ 14

Дата опубликования описания 06.07.76 (51) М. Кч G 06F 7/385

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.3(088.8) (72) Авторы изобретения

А. И. Журавлев и Б. С, Масленников

Особое конструкторское бюро вычислительной техники Рязанского радиотехнического института (») Заявитель (54) ПАРАЛЛЕЛЬНЫЙ СУММАТОР

Изобретение относится к вычислительной технике и может быть использовано при проектировании устройств ЦВМ и цифровой авто м а тики.

Известны параллельные сумматоры, содержащие в каждом разряде счетный триггер, элементы «И» и «ИЛИ», причем первые входы первого и второго элементов «И» соединены соответственно с первой и второй тактовыми шинами, а вторые входы — соответственно со входом разряда слагаемого и со входом переноса из младшего разряда, выходы пх подключены ко входам первого элемента

«ИЛИ», выход которого подключен ко входу счетного триггера, инверсный выход которого подключен к первому входу третьего элемента «И», второй вход которого соединен со входом разряда слагаемого, а выход — с пергзым входам второго элемента «ИЛИ», второй вход которого соединен с выходом четвертого элемента «И», первый вход которого соединен со входом переноса из младшего разряда, Известные сумматоры характеризуются критичностью к длительности тактовых импульсов (тт,и,) . Максимальная длительность тактового импульса (т, „.„анс ) не должна превышать времени переключения триггера и задержки на логических элементах «И» и

«ИЛИ». Если т, „соизмерима с глубиной задержки элементов сумматора, то может иметь место ложный перенос в последующий разр яд.

Целью изобретения является повышение надежности сумматора. В описываемом сумма5 торе это достигается тем, что в нем счетный триггер выполнен на триггерах с раздельными входамп, причем третий вход третьего элемента «И» соединен с выходом первого триггера с раздельными входами, а второй вход

10 четвертого элемента «И» соединен с инверсным выходом этого же триггера.

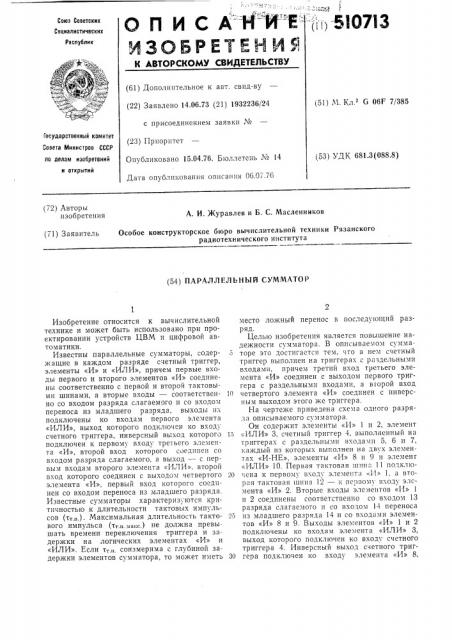

На чертеже приведена схема одного разряда описываемого сумматора.

Он содержит элементы «И» 1 и 2, элемент

15 «ИЛИ» 3, счетный триггер 4, выполненный на триггерах с раздельными входамп 5, 6 и 7, каждый из KQTopblx выполнен на двух элементах «И-НЕ», элементы «И» 8 и 9 и элемен г

«ИЛИ» 10. Первая тактовая пнин:", 11 подклю20 чена к первому входу элемента «И» 1. а вторая тактовая шина 12 — к перзому входу элемента «И» 2. Вторые входы элементов «И» 1 и 2 соединены соответственно со входом 13 разряда слагаемого и со вхоз,ом 14 переноса

25 из младшего разряда 14 и со входами элементов «И» 8 и 9. Выходы элементов «И» 1 и 2 подключены ко входам элемента «ИЛИ» 3, выход которого подключен ко входу счетного триггера 4. Инверсный выход счетного триг30 гера подключен ко входу элемента «И» 8, 510713 другой вход которого подключен к выходу триггера с раздельными входами 5. Инверсный выход триггера с раздельными входами 5 подключен ко входу элемента «И» 9. Выходы элементов «И» 8 и 9 подключены ко входам элемента «ИЛИ» 10, выход которого является выходом 15 переноса из данного разряда. Выход

16 счетного триггера является выходом данного разряда.

Суммирование осуществляется в два такта.

В первом такте слагаемое передается на вход счетного триггера. В каждом разряде сумматора формируются поразрядные суммы S,;, переносы С;, сформированные непосредственно в i-x разрядах, и происходит распространение переносов вдоль цепи сквозного переноса, состоящей из элементов «И» 9 и «ИЛИ» 10.

Перенос П; из -ro разряда осуществляется по формуле

П,=Si А,VS, П,.„ где А; — i-й разряд слагаемого;

П; — перенос, поступивший в i-и разряд из предыдущего разряда.

Во втором такте переносы, распространившиеся вдоль цепи сквозного переноса, поступают на входы счетчика триггеров соответствующих разрядов сумматора и изменяют их состояние.

Во втором такте во время переключения риггеров с раздельными входами соответствующие схемы формирования переносов (элементы «И» 8 и 9) блокируются сигналами с плеч триггера с раздельными входами 5. Бло кировка снимается по заднему фронту тактового импульса. Этим предотвращается возникновение ложных переносов.

Формула изобретения

Параллельный сумматор, содержащий в каждом разряде счетный триггер, элементы

1о «И» и «ИЛИ», причем первые входы первого и второго элементов «И» соединены соответственно с первой и второй тактовыми шинами, а вторые входы — соответственно со входом разряда слагаемого и со входом переноса из

15 младшего разряда, выходы их подключены ко входам первого элемента «ИЛИ», выход которого подключен ко входу счетного триггера, инверсный выход которого подключен к первому входу третьего элемента «И», второи

20 вход которого соединен со входом разряда слагаемого, а выход — с первым входом второго элемента «ИЛИ», второй вход которого соединен с выходом четвертого элемента «И», первый вход которого соединен со входом пе25 реноса из младшего разряда, о т л и ч а юшийся тем, что, с целью повышения надежности сумматора, счетный триггер выполнен на триггерах с раздельными входами, причем третий вход третьего элемента «И» соединен

30 с выходом первого триггера с раздельными входами, а второй вход етвертого элемента

«И» соединен с инверсным выходом этого же триггер а.

510713

Г

Составитель В. Березкин

Текред Т. Трусова

1;орр::..тор Л. Га".азова

1зеда1стор Л. Струве

Типография, пр. Сапуиоза, "

Заказ 1798)8 Изд. № 1271 Тираж 882 Подписное

ЦНИИПИ Государственного комитета Совета Миш строп СССР по делам изобретений и открьггий

113035, Москва, К-35, Раушская наб., д. 4/5