Модель узла сеточной области

Иллюстрации

Показать всеРеферат

О П И C А Н И Е „„SIOZ26

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 20.05.74 (21) 2027601/24 с присоединением заявки М (23) Приоритет

Опубликовано 15.04.76. Бюллетень М 14

Дата опубликования описания 10.06.76

Государственный комитет

Совета Нинистров СССР по делам изобретений и открытий (53) УДК 681.333(088 8) (72) Авторы изобретения

Б. А. Борковский, А. Ф. Катков и В. П. Раманцов

Институт электродинамики АН Украинской ССР (71) Заявитель (54) МОДЕЛЪ УЗЛА СЕТОЧНОЙ ОБЛАСТИ

Изобретение относится к электрическому моделированию.

Известна модель узла сеточной области, содержащая многоразрядный комбинационный сумматор, выходы которого подключены к соответствующим входам множительного устройства, к другим входам которого подключен первый вход модели.

Предложенная модель отличается тем, что, с целью увеличения точности моделирования, она содержит цифровой интегратор, первая группа входов которого подключена к выходам многоразрядного комбинационного сумматора и к выходам модели, а вторая группа входов — ко второму входу модели, и группу элементов «НЕ», выход которой соединен с первой группой входов многоразрядного комбинационного сумматора, со второй группой входов которого соединены выходы множительного устройства, другие входы многоразрядного комбинационного сумматора соединены с соответствующим входом модели, а выходы цифрового интегратора подключены ко входам группы элементов «НЕ».

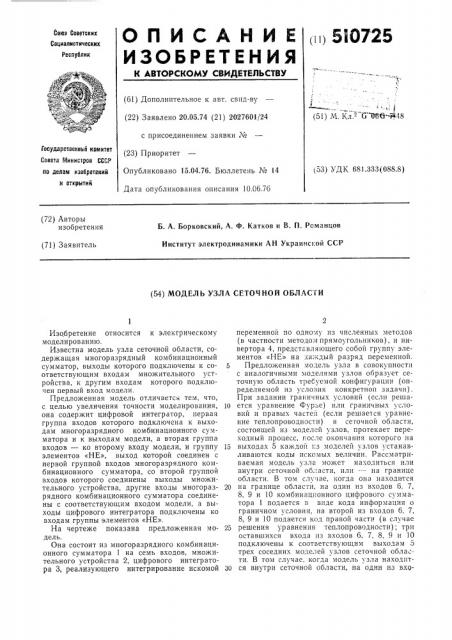

На чертеже показана предложенная модель.

Она состоит из многоразрядного комбинационного сумматора 1 на семь входов, множительного устройства 2, цифрового интегратора 3, реализующего интегрирование искомой переменной по одно . ó из численных методов (в частности методом прямоугольников), и инвертора 4, представляющего собой группу элементов «НЕ» на каждый разряд переменной.

5 Предложенная модель узла в совокупности с аналогичными моделями узлов образует сеточную область требуемой конфигурации (определяемой из условия конкретной задачи) .

При задании граничных условий (если реша10 ется уравнение Фурье) или граничных условий и правых частеи (если решается уравнение теплопроводности) в сеточной области, состоящей из моделей узлов, протекает переходный процесс, госле окончания которого на

15 выходах 5 каждой кз моделей узлов устанавливаются коды искомых величин. Рассматриваемая модель узла может находиться или внутри сеточной области, или — на границе области. В том случае, когда она находится

20 на границе области, на один из входов 6, 7, 8, 9 и 10 комбинационного цифрового сумматора 1 подается в виде кода информация о граничном условии, на второй из входов 6. 7, 8, 9 и 10 подается код правой части (в случае

25 решения уравнения теплопроводности); три оставшихся входа из входов 6, 7, 8, 9 и 10 подключены к соответствующим выходам 5 трех соседних моделей узлов сеточной области. В том случае, когда модель узла находит30 ся внутри сеточной области, на один из вхо510725

Составитель Е. Тимохина

Техред Т. Трусова

Корректор А. Галахова

Редактор Л. Тюрина

Заказ 1158/9 Изд. № 1271 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-З5, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 дов 6, 7, 8, 9 и 10 подается в виде кода информация о правой части моделируемого уравнения (в случае, когда решается уравнение

Фурье, — правая часть равна нулю), а четыре оставшихся входа 11 — 14 подключены к соответствующим выходам 5 четырех соседних моделей узлов сеточной области.

Формула изобретения

Модель узла сеточной области, содержащая многоразрядныЙ комбинационный cvMiMBтор, выходы которого подключены к соответствующим входам множительного стройства, к другим входам которого подключен первый вход модели, отличающаяся тем, что, с целью увеличения точности моделирования, она содержит цифровой интегратор, первая группа входов которого подключена к выходам многоразрядного комбинационного сум5 матора и к выходам модели, а вторая группа входов — ко второму входу модели, и группу элементов «НЕ», выход которой оединен с первой группой входов многоразрядного комбинационного сумматора, со второй группой

10 входов которого соединены выходы множительного устройства, другие входы многоразрядного комбинационного сумматора соединены с соответствующим входом модели, а выходы цифрового интегратора подключены ко

15 входам группы элементов «НЕ».