Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ бова йветекик

Социалистичвекик

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 25.10.74 (21) 2070715/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.04.76. бюллетень № 14

Дата опубликования описания 28.06.76

Государственный комитет

Совета Министров СССР йо делам изобретений и открытий (72) Авторы изобретения

Е. Н. Морозов и Г. М. Лукашев (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике и может быть использовано для запоминания изменяющегося во времени напряжения аналогового сигнала любой полярности.

Известно аналоговое запоминающее устройство, содержащее операционный усилитель, охваченный обратной отрицательной связью, ключ на МОП-транзисторах, выход которого соединен с входом истокового повторителя и накопительным элементом, например одной из обкладок конденсатора, другая обкладка которого подключена к шине нулевого потенциала.

Недостатком известного аналогового запоминающего устройства является недостаточное быстродействие в момент запоминания напряжения.

Целью изобретения является повышение быстродействия анологового запоминающего устройства.

Это достигается тем, что предлагаемое устройство содержит корректирующую цепь, два пассивных элемента, эмиттерный повторитель и дополнительный ключ на МОП-транзисторе, вход которого через один пассивный элемент соединен с инвертирующим входом и через корректирующую цепь с неинвертирующим входом операционного усилителя, выход которого через эмиттерный повторитель подключен к входу ключа на МОП-транзисторах и через дополнительный ключ на МОП-транзисторе и другой пассивный элемент соединен с выходом истокового повторителя и выхо5 дом устройства, вход которого соединен с входом корректирующей цепи.

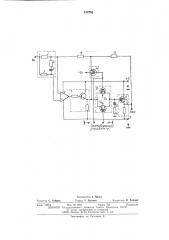

На чертеже приведена схема описываемого устройства, содержащего корректирующую цепь 1, выполненную на резисторах 2, 3, 4 и

10 конденсаторе 5, операционный усилитель 6, эмиттерный повторитель 7, ключ 8 на МОПтранзисторах с противоположным типом проводимости канала, истоковый повторитель 9, используемый в качестве накопительного эле15 мента запоминающий конденсатор 10, одна из обкладок которого соединена через резистор 11 с шиной нулевого потенциала, пассивные элементы резисторы 12, 13, к общей точке которых подключен вход дополнитель20 ного ключа 14 на МОП-транзисторе.

Схема работает следующим образом, Входной сигнал, подлежащий запоминанию, подается через резисторы 2 и 3 одновременно на оба входа операционного усилителя 6. В ре25 жиме запоминания ключ 8 открыт, а ключ 14 закрыт. Цепь обратной связи замыкается через эмиттерный повторитель 7, ключ 8, истоковый повторитель 9 и резисторы 12 и 13.

Запоминающий конденсатор 10 заряжается

30 до напряжения, при котором напряжение на

510752 выходе устройства (выход истокового повторителя) будет равно входному. Действительно, коэффициент передачи по неинвертирующему входу равен

12 !3 (1)

Коэффициент передачи по инвертирующему входу равен

К 12+ 13 (2) 2

Результирующее напряжение на выходе будет

U,„„== U,„(Ê, + К,) = U,„. (3)

Ошибкой за счет смещения уровней на эмиттерном повторителе 7 и истоковом повторителе 9 можно пренебречь, поскольку она уменьшается в коэффициент усиления разомкнутого операционного усилителя раз.

Благодаря наличию резистора 11 цепочка, состоящая из открытого ключа 8 на МОП-транзисторах и запоминающего конденсатора 10, имеет характеристику пропорционально интегрирующего фильтра и не вносит больших фазовых сдвигов на высоких частотах, что улучшает устойчивость схемы в режиме запоминания.

В режиме хранения ключ 8 закрывается, а ключ 14 открывается, замыкая цепь обратной связи через резистор 13. В силу приведенного выше соотношения /3/ напряжение на входе ключа 8 в режиме хранения будет поддерживаться равным входному, а операционный усилитель не перейдет в режим насыщения.

Благодаря этому время перехода из режима хранения в режим запоминания уменьшается, что увеличивает быстродействие схемы.

Благодаря наличию корректирующей цепи 1 на входе операционного усилителя, состоящей из резисторов 2, 3, 4 и конденсатора 5, а также резисторов 12, 13, напряжение на конденсаторе 5 будет в коэффициент усиления разомкнутой петли обратной связи раз меньше входного сигнала. Это обеспечивает быстрый перезаряд конденсатора 5 при изменении входного сигнала или изменении режима, а также предотвращает насьпцение каскадов операционного усилителя, что повышает быстродействие схемы. Составной ключ

8 на комплементарных МОП-транзисторах исключает зависимость результирующего сопротивления открытого ключа от уровня и полярности входного сигнала, что стабилизи5

50 рует параметры цепи обратной связи и, следовательно, улучшает устойчивость схемы.

Кроме того, компенсируются паразитные напряжения на запоминающем конденсаторе за счет заряда его фронтами управляющих напряжений через емкости затвор-исток МОПтранзисторов ключа 8, так как управляющие напряжения на их затворах должны быть противофазны.

Благодаря тому, что входная клемма соединена через резисторы 2 и 3 корректирующей цепи 1 с обоими входами операционного усилителя, коэффициент усиления схемы от входа до выхода всегда равен единице, независимо от величины сопротивления в цепи обратной связи. Поэтому включение дополнительного ключа 14 на МОП-транзисторе, замыкающего цепь обратной связи операционного усилителя на время хранения, нс дает возможности операционному усилителю перейти в режим насыщения, а к моменту следу1ощей записи на входе ключа 8 на МОПтранзисторах будет присутствовать напряжение, равное входному напряжению, до величины которого должен зарядиться запоминающий конденсатор во время записи. Благодаря этому увеличивается быстродействие схемы.

Формула изобретения

Лналоговое запоминающее устройство, содержащее операционный усилитель, охваченный обратной отрицательной связью, ключ на МОП-транзисторах, выход которого соединен с входом истокового повторителя и накопительным элементом, например одной из обкладок конденсатора, другая обкладка которого подключена к шине нулевого потенциала, отличающееся тем, что, с целью повышения оыстродействия, устройство содержит корректирующую цепь, два пассивных элемента, эмиттерный повторитель и дополнительный ключ на МОП-транзисторе, вход которого через один пассивный элемент соединен с инвертирующим входом и через корректирующую цепь с неинвертирующим входом операционного усилителя, выход которого через эмиттерный повторитель подключен к входу ключа на МОП-транзисторах и через дополнительный ключ на МОП-транзисторе и другой пассивный элемент соединен с выходом истокового повторителя и выходом устройства, вход которого соединен с входом корректирующей цепи, 72

1

Fpemudc7рахю; улгаУл ю- е

Составитель E. Пацук

Техред Т. Трусова

Корректор О. Тюрина

Редактор С. Хейфиц

Типография, пр. Сапунова, 2

Заказ 1407/4 Изд. № 1354 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

1!3035, Москва, Ж-35, Раушская наб., д. 4/5