Логическая схема "или-и-не"

Иллюстрации

Показать всеРеферат

ОПИСЛНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ i.) 510784

Союз Советских

Социалистических

Республик

/

1 " /, :,!,"".: i

-:- и (51) М, Кл. - Н ОЗК 19 10 (61) Дополнительное к авт. свид-ву (22) Заявлено 29.03.74 (21) 2009704, 26-21 с присоединением заявки №

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325.65 (088.8) Опубликовано 15.04.76. Бюллетень № 14

Дата опубликования описания 08.06.76 (72) Авторы изобретения

В. E. Мельник и Г. С. Мельник

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель (54) ЛОГИЧЕСКАЯ СХЕМА «ИЛИ вЂ” И вЂ” НЕ»

Государственный комитет (2 Приоритет

Изобретение относится к вычислительной технике и может использоваться при построении быстродействующих устройств ЦВМ.

Известны логические схемы «ИЛИ вЂ” И—

НЕ», содержащие диодную схему «ИЛИ вЂ” И», выход которых через туннельный диод вспомогательного триггера соединен с входом туннельно-транзисторного триггера и с инверсным выходом усилителя тока на диодах с накоплением заряда с парафазными выходами, прямой выход которого через туннельный диод подключен к общей шине.

С целью повышения быстродействия, помехоустойчивости и обеспечения возможности совместной работы схемы с потенциальными элементами в ней дополнительно установлены диод и транзистор с подключенными к его эмиттеру резистором и опорным диодом, причем диод включен между токозадающим резистором и туннельным диодом туннельнотранзисторного триггера, база транзистора соединена с прямым выходом усилителя тока на диодах с накоплением заряда, коллектор транзистора подключен к точке соединения дополнительного диода и токозадающего резистора туннельно-транзисторного триггера, второй вывод опорного диода соединен с общей шиной, а второй конец эмиттерного резистора подключен к шине питания.

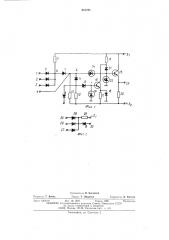

На фиг. 1 показана логическая схема

«ИЛИ вЂ” И вЂ” НЕ» без возврата к нулю; на фиг.

2 — схема диодного расширителя.

Логическая схема «ИЛИ вЂ” И вЂ” НЕ» содержит входы схемы 1, 2 и 3, вход 4 служит для подключения диодного расширителя. Входные диоды 5, резистор 6 и источник питания — E< образуют схему сборки единичных (положительных) сигналов. Диод 7 и диод 8 рас10 ширителя образуют схему совпадения для положительных сигналов, через разделительный диод 9 подаются отрицательные импульсы питания на диодный усилитель тока с парафазным выходом, собранный на резисторе

15 10 и диодах 11 и 12 с накоплениеM заряда.

Резистор 13 и туннельный диод 14 образуют вспомогательный триггер для повышения помехозащищенности схемы. Транзистор 15, туннельный диод 16, регистор 17 и опорный ди20 од 18 составляют схему установки триггера в низковольтное состояние.

Резисторы 19, 20, диод 21, туннельный диод 22 и транзистор 23 составляют бистабильный триггер для хранения и выдачи сигнала

25 на выход 24. Диодный расширитель содержит входы 25 — 27, диоды 28, 8 и резистор 29, подключенный к источнику Å . Выход расширителя 30 подключается к входу 4 логической схемы при необходимости образования схе30 мы «И».

510784

Схема работает следующим образом.

Предположим, что триггер на туннельном диоде 22 в начале первого такта находится в пулевом (низковольтном) состоянии.

При подаче на все входы нулевых сигналов входные диоды оказываюгся закрытыми и отрицательный ток стока — Ei — резистор

6, переключаясь в диод 7, устанавливает триггер на тунельном диоде 14 в низковольтное состояние, в результате чего по окончании прохождения отрицательного импульса, подаваемого в точку В, через диод с накоплением заряда 11 в течение первого такта протекает ток прямого смещения. Этот ток и концу первого такта обеспечиваст накопление в базе диода 11 заряда 0ь Ток в диоде 12 накопления заряда отсутствует, заряд в его базе не накапливается, что достигается обеспечением небольшого отрицательного потенциала в точке Б (порядка — 0,3 В) регулировкой тока стока — Е, — резистор 6, Поступающий в начале второго полутакта через диод 9 отрицательный синхроимпульс, рассасывая заряд 0ь вызывает протекание большого обратного тока через диод 11 и туннельный диод 14 на туннельный диод 22, в результате чего последний переключается в высоковольтное состояние, а на выходе 24 появляется единичный сигнал. В этом состоянии туннельно-транзисторный триггер находится в течение второго такта.

Если на вход схемы поступает единичный (положительный) уровень, то соответствующий входной диод 5 открыт, и него проходит ток стока — E> — резистор 6. Диод 7 закрывается. Положительным током через резистор 13 туннельпый диод 14 переключается в высокоcocToBHrIe. ПоявлеHHe положительного напряжения в точке Б приводит к запи- ранию диода с накоплением заряда 11 и переключению тока истока — E> — резистор 10 в диод 12. Прямой ток диода 12 протекает через обратносмещенный и имеющий малое сопротивление туннельный диод 16. Этот ток к концу второго такта обеспечивает накопление в базе диода 12 с накопителем заряда Оь

Поскольку ток, проходя через диод 11, отсутствует во втором такте, то заряд в его базе также отсутствует. Приходящий в начале третьего такта через диод 9 отрицательный синхроимпульс рассасывая заряд 0ь вызывает протекание большого обратного тока через диод 12. Величина этого тока превышает значение пикового тока туннельного диода

16. Последний переключается в высоковольтное состояние, формируя в точке Г отрицательный импульс.

Транзистор 15 положительным напряжением, создаваемым с помощью опорного диода

18 и резистора 17, в исходном состоянии выводится на грань отпирания, и появление отрицательного импульса на базе приводит к резкому отпиранию транзистора 15, в результате ток смещения туннельного диода 22, задаваемый стоком — Е, — резистор 19, переключается в коллекторную цепь транзистора

15, что приводит к переключению туннельного диода 22 в низковольтное состояние, а на выходе 24 появляется нулевой сигнал.

Если на входе схемы продолжает оставаться единичный сигнал, то переключение туннельно-транзисторного триггера осуществляется только при изменении информации на выходе диодной ложки.

При неизменной входной информации (серия нулей или серия единиц) выходная информация представлена потенциальным уровнем, что позволяет достаточно просто согласовывать выход предлагаемой схемы с входами различных потенциальных элементов.

Формула изобретения

Логическая схема «ИЛИ вЂ” И вЂ” НЕ», содержащая диодную схему «ИЛИ вЂ” И», выход которой через туннельный диод вспомогательного триггера соединен с входом туннельнотранзисторного триггера и с инверсным выходом усилителя тока на диодах с накоплением заряда с парафазными выходами, прямой выход которого через туннельный диод подключен к общей шине, отличающаяся тем, что, с целью повышения быстродействия, помехоустойчивости и обеспечения возможности совместной работы схемы с потенциальными элементами, в ней дополнительно установлены диод и транзистор с подключенными к его эмиттеру резистором и опорным диодом, причем диод включен между токозадающим резистором и туннельным диодом туннельнотранзисторного триггера, база транзистора соединена с прямым выходом усилителя тока на диодах с накоплением заряда, коллектор транзистора подключен к точке соединения дополнительного диода и токозадающего резистора туннельно-транзисторного триггера, второй вывод опорного диода соединен с общей шиной, а второй конец эмиттерного резистора подключен к шине питания.

510784

2

2В Z9

Составитель Н. Баринова

Texред T. Лященко

Редактор Т. Янова

Корректор Л. Котова

Типография, пр. Сапснова 2

Заказ 1204/!8 Изд, № 1259 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рамшская наб., д. 4i5