Устройство передачи данных

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (и! 510794 союз LîâåòñêèI!

Социалистических

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 23.03.73 (21) 1896772/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 15.04.76, Бюллетень ¹ 14

Дата опубликования описания 19.05.76 (51) М. Кл Н 04L 1/10

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.394.5 (088.8) (72) Автор изобретения

Э. А. Сукачев

Одесский электротехнн-.еский институт связи им. А. С. Попова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ

Изобретение относится к системам передачи данных и может быть использовано для высокоскоростной передачи дискретных сигналов по каналам связи.

Известно устройство для передачи данных, содержащее последовательно соединенные источник двоичных сигналов, формирующий фильтр, канал связи, стробирующий блок с генератором тактовых импульсов и пороговую схему, один выход которой через инвертор подключен к одному из входов первой выходной схемы ИЛИ, а другой выход непосредственно подключен к одному из входов второй выходной схемы ИЛИ. Недостатками такого устройства являются сложность кодирующего устройства и значительные межсимвольные искажения.

Для уменьшения межсимвольных искажений и упрощения схемы в предлагаемом устройстве на приемном конце введен узел запоминания знака импульсов, имеющий триггер, один вход которого соединен через линию задержки с выходом схемы ИЛИ, один вход которой связан с выходом инвертора, а другой вход соединен с выходом первой схемы И и другим входом первой выходной схемы ИЛИ, при этом другой вход триггера соединен через линию задержки с выходом схемы ИЛИ, один вход которой подключен к выходу пороговой схемы, а другой вход соединен одновременно с выходом второй схемы 11» друп1м входом второй вы. одной схемы ИЛИ, причем выходы инвертора н пороговой схемы через схему ИЛИ подключены к одному входу схемы запрета, другой вход которой подключен к выходу тактового генератора, а выход связан с одними входами схем И, прн этом другой вход первой схемы 1Л подключен к одному выходу триггера, а другой вход второй

10 схемы И вЂ” к другому выходу триггера.

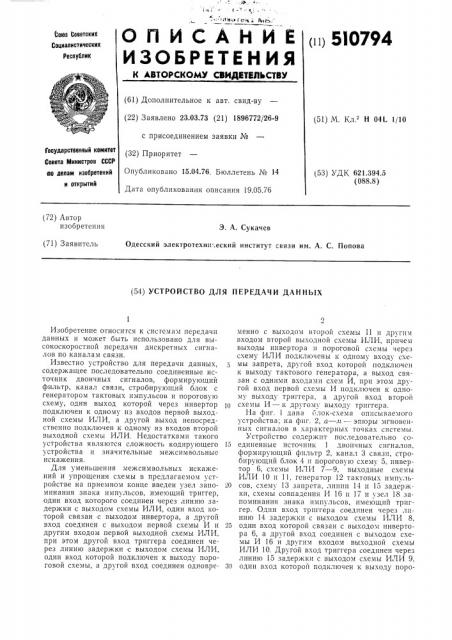

На фиг. 1 дана блок-схема описываемого устройства: на фиг. 2, а —.м — эпюры мгновенных сигналов в характерных точках системы.

Устройство содержит последовательно со15 еднненные источник 1 двоичных сигналов, формирующий фильтр 2, канал 3 связи, стробирующий блок 4 н пороговую схему 5, инвертор 6, схемы ИЛИ 7 — 9, выходные схемы

ИЛИ 10 и 11, генератор 12 тактовых импуль20 сов, схему 13 запрета, линии 14 н 15 задержки, схемы совпадения И 16 н 17 и узел 18 запоминания знака импульсов, имеющий триггер. Один вход триггера соединен через линию 14 задержки с выходом схемы ИЛИ 8, 25 один вход которой связан с выходом инвертора 6, а другой вход соединен с выходом схемы И 16 и другим входом выходной схемы

ИЛИ 10. Другой вход триггера соединен через линию 15 задержки с выходом схемы ИЛИ 9, 30 один вход которой подключен к выходу поро510794 говой схемы 5, а другой вход соединен одновременно с выходом схемы И 17 и другим входом выходной схемы ИЛИ 11. Выходы инвертора 6 и пороговой схемы 5 через схему ИЛИ

7 подключены к одному входу схемы 13 запрета, другой вход которой подключен к выходу тактового генератора 12, а выход связан с одними входами схем И 16 и 17. При этом другой вход схемы И 16 подключен к одному выходу триггера 18, а другой вход схемы И

17 — к другому выходу триггера.

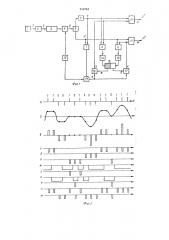

Двоичный и многоуровневый сигналы показаны на фиг. 2,а и б, оответственно.

Устройство работа т следующим образом.

С выхода стробпрующего блока 4 приемника двухполярные импульсы разных уровней (см. фиг. 2,в) поступают на пороговую схему 5.

Оба положительны.; уровня соответствуют передаче «1». После инвертора 6 отрицательные импульсы поступают на выходную схему

ИЛИ 10 (см. фиг. 2,г). Наличие инвертора 6 позволяет оперировать в приемнике с импульсами одной (отрицательной) полярности, что упрощает схему.

Оба отрицательных уровня соответствуют передаче «О», поэтому с выхода пороговой схемы 5 отрицательные импульсы поступа от непосредственно на вь|ходн ю схемс ИЛИ 11 (см. фиг. 2,д) .

Нулевой уровень в принимаемом сигнале соответствует передаче «1» или «О» в зависимости от того, какой символ передавался перед этим. Поэтому для правильно-о декодирования нулевого уровня требуется устройство запоминания знака предыдущего импульса, в качестве которого и используется триггер 18 с раздельным запуском, управляемый через схемы ИЛИ 8 и 9.

При отсутствии импульсов на двух выходах пороговой схемы 5, что бывает прп приеме нулевого уровня, на схему 13 запрета не подается запрещающий импульс и на схемы И 16 и 17 поступает импульс от тактового генератора 12 (см. фиг. 2,е).

Триггер 18 помнит знак предыдущего импульса, что проявляется в виде отрицательного потенциала, который подается на;. одну из схем И 16 или 17 и способствует прохождению импульса от г нератора 12 на выход приемника. Если нулевому уровню предшествовал отрицательный, то работает схема И 16, импульс от генератора 12 пост пает на выходную схему ИЛИ 10 и приемник фиксирует прием «1» (см. фиг. 2, ж, з). Этот же импульс подается через схему ИЛИ 8 и линию 1:задержки на триггер 18 для изменения его состояния, что эквивалентно запоминанию положительного знака. При этом к работе подготавливается схема И 17.

Лналогично декодируется нулевой уровень

1О прп передаче «О» (см. фиг. 2,и, к ), Таким образом, при любом сочетании «!» и

«О» на передаче приемник безошибочно декодирует принимаемый многоуровневый сиги ал, преобразуя его снова в двоичную форму (см. !

5 фиг. 2, л, л).

Формула изобретения

20 Устройство для передачи данных, содержащее последовательно соединенные источник двоичных сигналов, формирукгщий фильтр, канал связи, стробирующий блок с генератором тактовых импульсов и пороговую схем), 25 один выход которой чсрез пнвертор подключен к одному из входов первой выходной схемы ИЛИ, а другой выход подключен непосредственно к одному пз входов второй выходной схемы ИЛИ, отл ич а югцееся тем, 30 что, с целью уменьшения межсимвольных искажений и упрощения схемы устройства, на приемном конце введен узел запоминания знака импульcîâ, имеющий триггер, один вход которого соединен через лини:о задержки с

З выходом схемы «ИЛИ», один вход которой связан с выходом инвертора, а другой вход соединен с выходом первой схемы И и другим входом первой выходной схемы ИЛИ, при этом другой вход триггера соединен через ли40 нию задержки с выходом схемы ИЛИ, один вход которой подключен к выходу пороговои схемы, а другой вход соединен одновременно с выходом второй схемы И и другим входом второй выходной схемы ИЛИ, причем выходы

45 инвертора и пороговой схемы через схему

ИЛИ подключены к одному входу схемы запрета, другой вход которой подключен к выходу тактового генератора, а выход связан с одними входами схем И, при этом другой вход .0 первой схемы И подключен к одному выходу триггера, а другой вход второй схемы И вЂ”вЂ” к дряз гом выход триггера.