Устройство фазового пуска

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ, (I I1 510798

«0300 Соегтсхкх

Сокиа!lистинескнк

Р000 Jëèê

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-в (51) М. 11л.г Н 04L 7/10

Н 04J 3/OG (22) Заявлено 16.07.73 (21) 1951066 09 с ПРI!ГовдI!11с1!13с3! 3 IЯ13к!! ¹ (23) Приоритет

Опубликова:o 15.04.76. Б!Ог!летспь М !4,- Г

C )-- «./. Ссударстегнный комитет

Сонета Министроа СССР оо делам изобретений и открытий (53) УДК 621.394.662 (088.8) Дтата оп. бликов",Ièÿ o!1!r.ан!гя 25.05.76 (72) Лвтор !

13063рс I CIIIIH

А. М. Че1рнь!н1 (71) Заяшгтсл!> (54) YCTPORCTBO ДЛЯ ФАЗОВОГО 11УСКА

Изобретение относится к электросвязи и может использоваться в системах передачи и приема дискретной информации.

Известно устройство для фазового пуска, содержащее счетчик ошиоок и регистр сдвига с сумматором в цепи обратной связи, причем выходы регистра сдвига через селекторы подключены к входам блока управления.

Однако известное устройство имеет низкую помехоустойчивость вследствие or раниченного числа корректируемых ошибок по сравненшо потенциально возможным чи:лом.

Цель изобретения — — повышение помехоустойчивости.

Это достигается тем, что в предлагаемом устройстве между выходом счетчика ошибок и соответствующим входом блока управления включен блок последовательной регистрации, к другому входу которого подключен выход одного из селекторов через последовательно соединенные дополнительные ключи, схему логического сложения и распределитель.

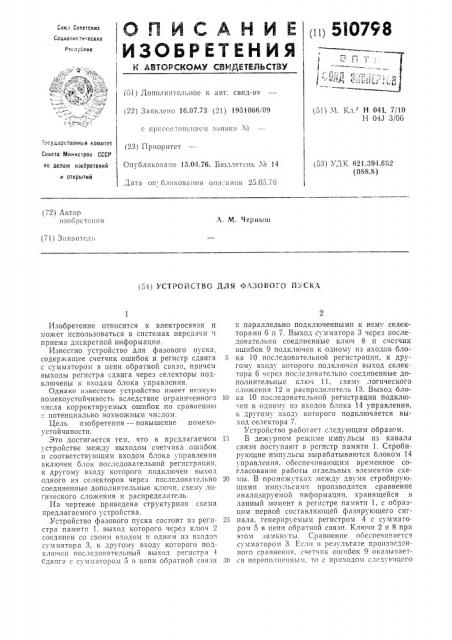

На чертеже приведена структурная схема предлагаемого устройства.

Устройство фазового пуска состоит из регистра памяти 1. выход которого через ключ 2 соединен со своим входом и одним из входов сумматора 3, к другому входу которого подключен последовательный выход регистра 4 сдвига с сумматором 5 !3 цепи обратной связи п параллельно подключенными к нему селекторами 6 и 7. Выход сумматора 3 через последовательно соединенные ключ 8 и счетчик ошибок 9 подкспочен к одному из входов бло5 ка 10 последовательной регистрации, к другому входу которого подключ í выход селектора 6 через последовательно соединенные дополнительные ключ 11, схему логического сложения 12 и распределитель 13. Выход бло10 IB 10 последовательной регистрации подключен к одному из входов блока 14 управления, к другому входу которого подключается вых од селе кто р а 7.

Устройство работаст следующим образом.

15 В дежурном режиме импульсы из канала связи поступают в регистр памяти 1. Стробирующие импульсы вырабатываются блоком 14 управления, обеспечивающим временное согласование работы отдельных элементов схе20 мы. В промежутках между двумя стробирующими импульсами производится сравнение анализируемой информации, хранящейся в данный момент в регистре памяти 1, с образцом первой составляющей фазирующего сиг25 нала, генерируемым регистром 4 с сумматором 5 в цепи ооратной связи. Кл!Очи 2 и 8 при этом замкнуты. Сравнение обеспечивается сумматором 3. Есл!! â результате произведеHного сравнения, счетчик ошибок 9 оказыгает30 ся перепо!rrc «Ir! 13!, то с приходом следмющсго

510798

Составитель P. Дубовая

Те. ред Т, Лященко

Корректор А. Дзесова

Редактор И. Шубина

Заказ 1108/10 Изд. ¹ 1264 Тираж 864 Подпис!(ое

Ц11ИИПИ Государственного комитета Совета Министров ГГГР по делам изобре!еиий и откр!ятий

113035, Москва, )К-35, Раущская иаб.,,l. 4, 5

Тииогра(рия, !if). C li!) иова, 2 стробирующего импульса устройство вновь

j)II00TBPT 13 30)I(j 1)110)I pc)l(ll)l . Емкос(ь c IcT IIIl(B 0 ш И 0 0 1:. 9 р (1 в и а I I 0 T C II L(I! II, пи о 130 3 )1 0 ж и О м у количеству корректнрусмых ошибок. Если счетчик ошибок 9 оказывается незаполненным, то устройство переходит в с,(едующии режим. При этом, тактовое питанис регистров

1 и 4 осуществляется стробирующими импульсами, кл!оч 2 разомкнут, а кл!оч 8 замкнуT.

Импульсы из канала постуIIBI01 в сумматор

3, а регистр 4 генерирует ооразцы второй и

ПОСЛСДМ10ЩИХ CO TH!3;IHIOIIIHX (j) L)3!Ij) N Юн(СГО сигнала. Селектор 6 вырабатывает сигналы об окончашш формирования образцов второй и последх lощпх со" та в, !silo(((I!õ фа "a!pi lоlцсГО сигнала, которые поступают в олок 10 последовательной регистрации, обеспс: ивающий последовательную регистрапшо этих составляющих с точностью до такта в зависимост:I от состояний счетчика ошибок 9.

Если в процессе приема второй и послсдуloщих составляющих фазирующего сигнала счетчик ошибок 9 оказывается переполненным. то все устройство переводится в дежурный ре)кпм работы.

11ыход селектора 6 через кгпоч 11 соединен .:о схемой логического сложения 12, выхг)т коT0P0ii ПО, (I(1ЮЧСН K СООТВ TCГВ) IОН(С)!У БХОДГ олока 10 поспело !И(ельной регистрации

)то Ооеспсчиваlс Г ре! исTp31(lii0 цик. lli i ских сдвигов ьторой и последующих оставл1!ющих фа:!ИруlощсГО снГП(1(!11 с Гоч ность!0 JO такта.

10 Формула изобретения

УстроЙство Q,"Iя фа 30130 Î

í(åå счетчик ошибок и регисгр сдвига с сумматором в цепи обратной связи. причем выхо15 ды регистра сдвига через селекторы подключены к входам блока управления, о т л и ч а-! о щ с е с я тем, что, с целью повышения помехоустойчивости, между выходом счетчика ошибок и соответствующим входом блока уlI20 равлепия включен блок последовательной регистрации, к другому входу которого подключeII выход одного из селекторов через последователь о соединенные допог(нительныс ключ, схему логического сло)кения и распре25 .(слитсги .