Приемное устройство электронного телеграфного аппарата

Иллюстрации

Показать всеРеферат

О П И C А Н И Е (i!1516865., ИЗОБРЕТЕН И Я

Сава Советскик

Социалистических

Республик

1. P!R р, р-рт т уу рц рЕтЕ П p у (61) Дополнительное и авт, свид-ву (22) Заявлено 17.12.73 (21) 1977291, 26-9 (51),1L Кл.- Н 04L 27 22 с присоединением заявки М (23) Г1риорнтст

Государственный комитет

Совета Министров СССР

Онубликоьано 15.04.76. Бюллетень ¹ 11 па делам изобретений (53 1 УДК 621.394.62 (688.8) и о;крыннн

l3TB онуолнкова ня онн анни 5.0 ...76 (72) A!3TOpl>I нзобрстс ня

В. М. Петров, С. С. Петров, В. 5. Ал.:eee в B. С, Гр;";ннн (! l) Заявите,lh (54) ПРИЕМ lOE УСТPOACTBO ЗЛЕ1<Т ОННОГО

ТЕЛЕГРАФНОГО АППАРАТА

Изобретение относится к телеграфной связи.

Известно приемное устройство электронного телеграфного аппарата, содержащее последовательно соединенные усилитель — ограничитель, распределитель, детектор, накопитель и выходной блок. Однако такое устройство имеет невысокую помехоустойчивость.

Для повышения помехоустойчивости в предлагаемом устройстве между усилителем— ограничителем и распределителем включена цепь из последовательно соединенных формирователя импульсов, схемы «Запрет» и элемента задержки, причем выход схемы «Запрет» дополнительно подключен к управляющему входу детектора, выход которого подключен ко второму входу распределчтеля, а второй выход формирователя через вторую схему «Запрет» подключен к управляющему входу накопителя, дополнительный выход которого через второй формирователь импульсов подключен к управляющим входам обеих схем «Запрет».

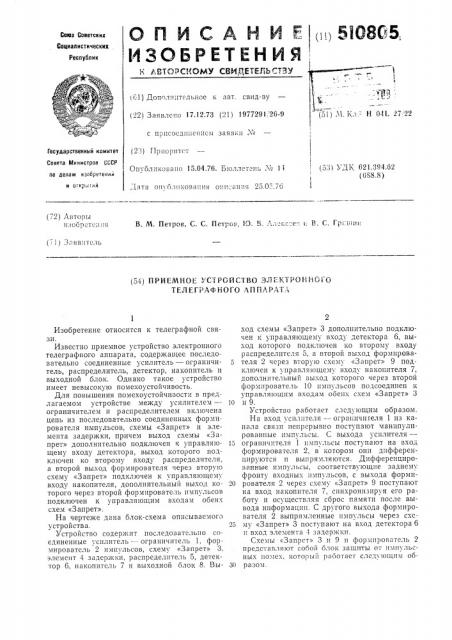

На чертеже дана блок-схема описываемого устройства.

Устройство содержит последовательно с0единенные усилитель — — ограничитель 1, формирователь 2 импульсов, схему «Запрет» 3, элемент 4 задержки, распределитель 5, детектор 6, накопитель 7 и выходной блок 8. Выход схемы «Запрет» 3 дополнительно подключен к управляющему входу детектора 6, выход которого подключен ко второму входу распределителя 5, а второй выход формирователя 2 через вторую схему «Запрет» 9 подключен к управляющему входу накопителя 7, дополнитсльHüø выход которого через второй формпрователь 10 импульсов подсоединен к управляющим входам обеих схем «Запрет» 3

10 и 9.

Устройство работает слсдующчм образом.

На вход усилителя — ограничнгеля 1 из канала связи непрерывно поступают манппулированные импульсы. С выхода усилителя—

15 ограничителя 1 импульсы поступают на вход формирователя 2, в котором они дифференцируются н выпрямляются. Дифференцированные импульсы, соответствующие заднему фронту входных импульсов, с выхода форми20 рователя 2 через схему «Запрет» 9 поступают на вход накопителя 7, сннхроннзируя его работу и осуществляя сброс памяти после вывода информации. С другого выхода формирователя 2 выпрямленные импульсы через схе25 му «Запрет» 3 поступают на вход детектора 6 и вход элемента 4 задержки.

Схемы «Запрст» 3 н 9 и формирователь 2 представляют собой блок защиты от импульсных помех, который работает следующим об30 разом.

510805 ((t ! — à (+ +

I (Зах()з 1108) 1Ч Изд. ¹ 12(«1 1 è р 2 >K 864

Т)!)(о",)! (р: я, пр. C:a!IX)I()âà, 2

Ц!П 1 И ПИ

11од!) Icllo(. (хогд(1 дстекторо;I зафиксирус Гся по;!ожсIIklC ПСрсдпСГО I!. 111 за IIIC! О фj)ОПТ!! Ilр ИПЯ ГОГÎ !!)!П>> ЛЬСс! H ИпфОР)12Ц1!Я За И ИШСТС51 В 11 cl«01111 тель 7, с выхода последнего Выда c;i cигиал

На фОР)!5!РОВс)тСЛЬ (О, «ОтОРЫй фОРМИРУСт i»l

П3 ЛЬС Д 711 1 С,! Ш!ОС ГЬ!О ИСС1<О.И>КО Х)с!И>!LlCй;! ИI11!XIсlЛЬЕ!ОЙ ДГ!11 ГЕ,1Ь110С И 13XОД!11>!". 11)IIIRTIЬСО>3

И Ilcl) 3. )TOT !»III \11Ü 130:3,70(ICÒB Cт 112, ."МЫ

«Запрет» 3 и 9 и закрывает тра <т Hpoxo>«дениЯ сиГна;13, прсДОхрап5151 схем i ирисл!никс! 10

ОТ ЗОЗДСЙСТЗИЯ И.">!ПХ ihCiibiX По)!СХ В ЭГО)! IIIIтсрвалс времени. (103TOx» дроблс)пге пер!)ого

ИЗ!ПУ. !ЬС2 H ИМПМГ!ьспс151 ПОМСХс! В HC()BOII II33ЗЕ НС ПP IBОJ 5IT К Ложной j)с!001 . СХС)lj I П()ИС М И 0 Г 0 C T P 0! I (1 13 2 . 15 ,=.)г!С)!Снт - . задержк)! задерживает пост3па!

ОЩПЕ kl2 СГО ВХОД И." !П ЛЬСЫ li3 ВРС!3151, ОПРСДСляемос минимальной длительностью ипформационного импмльса (памзь!). Вь!Ходнь!с импульсы его посту!i310T»3 вход распределите- 20 . 1 я 5. 3 3 с 11 р е д,:>;! и т с,1 ь 0 со в»! е c T! l 0 с д(1 т с к т ОРО)! 6 0()P: пс -IIIBc:с1 ii20>IP3тел!>п 10 РсГII "l Рапию по=ле lo 3Tc;ff поступак)щих па дстскТОР ИЗIПУ;lhCOB. Рс)СПРЕДСЛИТСЛЬ ) H)ICCT ДВ 1 входа и !НссТ зыхо!0B. Пере,7 поступ icii»cxi 25 на распрсде.;)игсль и)!Пульса с элемспта 4 за,1CP)I

1ектора 6 появ.!ястся сигll2л па выходе дстек гора, подкгно шшом к распре !3 IlcxO,TI!0(00с1 Ояиис ИОслс к(!ждои рсГ!1(! раиии IDIII i .1ьс- 1

i3 дс1 с«торс.

Б Накопитель 7 импульсil поступают в двух— элементном шссп(позиционном Ilocëåäîâàòñëüli 0 Ì КОД(., ПРИ С М 3 cl П ИСЬ И МНУ;1ЬСО 13, СОО! В cTB>i ющих HcpBoxl), разр5!д3 (положсни10 Ilcреднего фронта входного 1:мпуль а) и гггорому разряду (положению заднего фронта имИУЛЬСс!), ОСМЩССТ13. !51СТС51 I3;IB3 X (). IOK3X Ис!.) l )l 1 I I. (l2 накопителя шформация в параллсльIIOi>! ШСС ГИГIОЗИЦИОИИОМ Д13 > ХЭЛС:>1ЕНТИО)! КОДЕ пос 3 паст а Вь!ходной Олок 8, прсдстаВля!ОШии собой перскодирующсс устрои=тво и уcTРо!!СТВО 13hIBO+3 ИифоР М 3 ЦИИ.

Формула изобретения

Прис)!Нос устройство электронного Гелсгpa(j)IIo!0 аппарата, содержащее последовательно .оединснные усил))тель — ограничитель, распределитель, дсгс«тор, накопитель H

I3l>IXOIFIOII О. !ОК, 0 T;I И Ч 2 10 IH, С P С 51 ТЕМ, ЧТО, C iFC IhlO ПОВЫШСИИЯ l!Oi31(XON СТО!!с1 IBOCTH, IC)K ду усилителем ограничителем и распредслиl е. 1с)l 13кл!Очсна цспь из послсдоватсльно сосдинснны: формирователя 1!мп IhcoB, схемы

«Запрет» и элемента задержки, при ем выход схемы «Запрет» дополиительно подключен к уllp 2Вля юlцсм)у ВхОд де Гсктора, выход кОтОрого подключен ко второму входу распредс.)Ителя, а второй выход формирователя через

Втору«) cxcìó «Запрет» подклlo lcí к управляю)цсму входу накопителя. дополни Гельный выХ 0 Д K 0 TO P O ! С (: С 3 3 Т О, ) 0 1! ф 0 Р Ъ13! Р 0 !3 с) Т ЕЛ Ь И ) !ПМ.1ЬСОВ ПОДИ IIOÖCII К 3".ПРс!ЗГIЯЮIЦИ)l ВХОД23! оос) lx схем «3 а и рет».