Устройство для автоматического кодирования информации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистииеских

Республик (11) 5И585 (61) Дополнительное к авт. свид-ву» (22) Заявлено 22.04.74 (21) 2018500/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.04.74эюллетень №15 (45) Дата опубликования опнсання15.09 76 (51) М. Кл. С06Г 5/00

6 067 9/18

Государственный номнтет

Совета Мнннстрон СССР но делам нэаорвтеннй н открытнй (+) УДК 681.326(088.8) (72) Авторы изобретения

А. П. Самойленко и М. Д. Скубилин

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ ИНФОРМАЦИИ

Изобретение относится к вычислительной технике и может быть использовано в системах параллельной передачи многоэлементных сигналов.

Известны устройства для автоматического кодирования информации, содержашие формирователи, элементы памяти, дифференцируюшие узлы, блок кодирования, триггеры, элемент ИЛИ, одновибратор, причем входы устройства соединены со входами формирователей, выходы которых соединены с информационными входами элементов памяти, информационные выходы которых через дифференцируюшие узлы соединены со входами блока кодирования, выходы которого соединены с единичными входами триггеров и через элемент ИЛИ со входом одновибратора, выход которого соединен с нулевыми входами триггера и с управляюшими входами элементов памяти, выходы триггеров соединены с выходами устройства.

Цель изобретения — упростить устройство.

Это достигается тем, что в устройство введены дополнительные элементы ИЛИ, причем первый и второй входы каждого дополнительного элемента ИЛИ соединены соответственно с выходом одновибратора и с управляюшим выходом соответствующего элемента памяти, выход каждого дополнительного элемента ИЛИ соединен с управляюшим входом элемента памяти и третьим входом дополнительного элемента ИЛИ, стояших в цепях с меньшим приоритетом.

10 Это позволяет использовать идентичные элементы памяти и сократить число функциональных связей между элементами памяти.

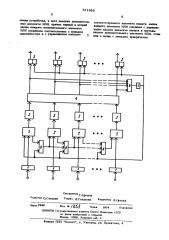

На чертеже изображена схема устройства для автоматического кодрования инфор15 мации.

Оно содержит формирователи 1, элементы памяти 2, дифференцируюшие узлы 3, блок кодирования 4, триггеры 5, элемент

ИЛИ 6, одновибратор 7, дополнительные

20 элементы ИЛИ 8. формирователи 1 пРедназначаютси дли формирования импульса от переднего фронта релейного сигнала объекта.

Элементы памяти 2 используют для запа2а сания информации о возникающих требованпях ня пеВЕДЯЧУ СО CTGOGIgg. ЮОП"-."--" "-- - .::l = - лей и работают в двух перестраиваемь: режимах", кратковременной и дма-овременнай памяти. Каждый элемент памяти состоит из симметричного триГГерB и злектрОИИОГО ключа. Режим долГОВременнОй памяти: электронный ключ закрыт, перестряивяемый элемент памяти работает В режиме триггера с двумя стойчнвымн cocTQBIIHIIMH. Режим

KPBTKGBPBMB&HIo1!iI НЯ1«? и "H злектРонный клк1ч 3О

Открыт, элемент 2 работает I K Одновибратор,, т. е., Обладает Одним устойчивым состоянием.

Исходное состояние элементов 2 — в режиме квятковременной памяти, Длитель- 35 ность Возбуркденного состояния Одноустойчивого триггера подбирают равной времени, достаточному для установления приоритетности кодировании сигнала с наименишим порядкОВым номером (BBcQM) среди зяфиксирОВан- ных элементами 2.

Управляюцц1м входом перестраиваемого элемента памяти 2 является вход электронHGro ключа. Элементы 2 подачей потенциBJIB на их упрявляюшио Вхсды перевОдятся в режим долговременной памяти, т. е. электронныи xIIIoч закрывается и IlpBQ6paзует Одноустойчивый трщтер и двухустойчивый путеу устранения ассимметричности плеч. Дри зтОм иняормяция. записанная В

Э

ЗО элементе памяти 2, не стирается, общее состояние триггера, соответствующее исХОДНОМУ СО» ОДЦЯЕТСД.

QII epBHIIHpyIolr me пепи 3 предназначены

И для формт1рования имп«ульса фронту Выходного импульса элементов 2.

Триггеры 5 служат для фиксирования кодовой комбинации =:,я BBBMII ппределяемое параметрами Одновибратора 7. При помощи

48 элементов ИЛИ 8 Осушествляется управлеHHB режимом рабОТЫ -IIBMBHTQB 2. яждому сообшению соответствует своя индивндуалъняа цепь, состоящая из формиpGBBTBJIH 1 р элемен га памяти 2, дифференцируюшего улла 3. Г1ри Отсутствии сигналов сообшений устройство находится в исходном a:còoHHèè,т- е. элементы 2 не возбуждены и нахОдятся В режиме краткОВременной памяти. При поступлении одного, ABACK II более сообщений Одновременно HIlll и любой последовательности соответствующие им репейные сигналы после формироВания их В импульсы по переднему фронту формирователями 1 фиксируются соответству юшими" элементами памяти 2, которые переходят B неус -GI1!HHBGB состояние режима кр1тковременной памяти.

Посредством функциональной связи, осушествляемой пОследовательнОй цепью эле- 6О

« эHTGB ИЛИ 8, Все последующие элементы

2 после элемента 2 t -той цепи, соответствукнцей L -тому сообщению с наименьшим номером среди поступивших, под воздействием потенциалов на их управляющие входы переводятся в режим долговременной памяТи, Возбужденный элемент памяти 2 цепи

1 -того сообщения, находящийся в режиме кратковременной памяти, возврашаясь и исходное состояние режима кратковременной памяти, воздействует задним фронтом импульса на вход блока кодирования 4. Кодовая комбинация, соответствующая -тому сообщению, фиксируется триггерами 5, при этом дизьюнктивный сигнал с выхода элемента ИЛИ 6 возбуждает одновибратор 7, тем самым определяется длительность кодовой посылки. Выходной потенциал одновибратора 7 переводит все элементы памяти 2 в режим долговременной памяти, т. е. в режим двухустойчивого триггера. Сообщения, возникающие во время кодирования фиксируются соответствующими элементами

2.

)До окончании времени кодирования одновибратор 7 возвращается в исходное состояние. Элементы памяти 2, включая элемент ю в котором было зафиксировано сообщение

О

Ф например (I1. +2), переходят в состояние кратковременной памяти, причем элемент 2 находится В возбужденном состоянии и при помощи элементов ИЛИ 8 элементы

2 с (L +3) до tL удерживаются в режиме триггера, т. е. долговременной памяти.

Процесс формирования кодовой посылки, соответствующей (i, + 2) -му сообщению, аналогичен описанному.

Введение элементов ИЛИ 8 позволяет упростить устройство. е ормула изобретения

Устройство для автоматического кодиро ванин информации, содержащее формирователи, элементы памяти, дифференцирующие узлы блок кодирования, триггеры элемент

ИЛИ, одновибратор, причем входы устройства соединены со входами формирователей, выходы которых соединены с информапионными входами элементов памяти, информационные выходы которых через дифференцирующие узлы соединены со входами блока кодирования, выходы которого соединены с единичными входами триггеров и через элемент ИЛИ со входом одновибратора выход которого соединен с нулевыми вхо дами триггеров и с управляющими Входами элементов памяти, выходы триггеров соединены с выходами устройства, о т л ич а ю ш е е с я тем, что, с целью упро81 1585

Составитель

Редактор <).Степина Техред ЛД ладкова корректор Л.Орлова

Язд. 1й /Д Я Тира к 554 Подписиое

Заказ 41

ЦНИИПИ Государственного комитета Совета Министров СССР ио делак изобретений и открытий

Москва, 113О35, Раушскак наб., 4

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 женим устройства, в него введены дааацнитель. ные элементы ИЛИ. причем первый и второй входы каждого дополнительное элемента

ИЛИ соединены соответственно с выходом одновибратора и с управлнюшим выходом соответствуюшего элемента памяти. выход каждого элемента ИЛИ соединен с унравла юшим входом элемента памати и третьим входом дополнительного элемента ИЛИ. стон. ших в цепах с меньшим приоритетом.