Устройство для деления чисел

Иллюстрации

Показать всеРеферат

О П И С А Н И Е () 511590

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 05.05.74(21) 2021931/24 с присоединением заявки №(23) Приоритет— (43) Опубликовано 25.04.76 Бюллетень ¹ 15 (45) Дата опубликования описания 07.07.77 (51) М, Кл, G 06 T 7/52

Государственный комитет

Соввта Министров СССР оо делам изооретений и открытий (53) УДК 681 3 (088.8) (72) Авторы изобретения

В. B. Немытов и А. М. Оранский (71) Заявитель

Минский радиотехнический институт (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ

Изобретение относится к вычислительной технике> особенно к специализированным вь числителям, и предназначено для выполнения операции деления двух чисел.

Известно устройство для деления чисел, содержащее многовходовой элемент И, регистр делимого, выход которого соединен со входом сумматора-вычитателя делимого, регистр делителя, выход которого соединен со входом сумматора-вычитателя делителя. щ

Однако для получения делимого у

= А-В необходимо проводить подготовитель ные операции, на что требуется дополнительное время; на каждом шаге вычислений не— 1 обходимо вычислять значения х; 2 и . у

Z, 2 причем возрастает с возрастаУ нием шага, что заставило для сокращения времени получения этих значений применить матричные сдвигатели, для реализации которых требуется большой объем оборудования; после каждого шага вычислений необходима передача содержимого сумматороввычитателей в соответствующие регистры, на что тратится дополнительное время вычислений. 25

Цель изобретения — сократить объем оборудования для упрощения устройства и пс высить быстродействие.

Это достигается тем, что в устройстве отсутствуют сдвигатели, - сумматор-вычитатель и регистр частного с соответствующими связями, а дополнительно в него введен блок управления, первый вход которого соединен с первым выходом сумматора-вычитателя делителя, вторые выходы которого через многовходовой элемент И соединены со вторым входом блока управления, выход которого подключен к управляющим входам всех сумматоров-вычитателей и регистров, при этом установочные входы регистра делимого и сумматора-вычитателя делимого подключены к первой шине входного сигнала, а установочные входы регистра делителя и сумматора-вычитателя делителя подсоединены ко второй шине входного сигнала.

Предлагаемое устройство отличается меньшими затратами на оборудование, высоким быстродействием при высокой точности вычислений. Время выполнения деления

5»5ЯО составляет величину 4 причем < 4 и ь ! где Т - время одного сложения (вычий тания), и - число шагов.

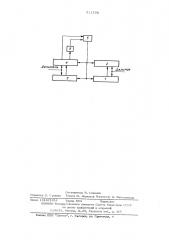

Устройство для деления чисел содержит регистр делимого 1, сумматор-вычитатель делимого 2, регистр делителя 3, сумматорвычитатель де в!теля 4, блок управления 5, многовходовой элемент И 6.

Пусть нужно выполнить деление а/Ь (а и в - нормализованные числа). Алгоритм вычислений запишется

0I =С! + Р О!

b, = b,, » r,. b z, 10 где + 1, при 1

1 IlpH g ) 1

7! !

О, при Ь, = 1 { останов)

Причем = 1, !!, При b;, = 1 на любом промежуточном шаге () !.! ) определяется значение частного и вычисления прекращаются, что сокращает время вычислений.

Устройство работает следующим образом.

В регистр делимого 1 и сумматор-вычитатель 2 заносится через объединенные установочные входы делимое "с» "; в регистр делителя 3 и сумматор-вычитатель 4 — делитель ")» ", также через свои объединенные входы. Занесение операндов с» " и " Ь " в регистры 1 и 3 производится со сдвигом на один -разряд, т.е. и регистры 1 и 3 сра— зу же заносятся значения с! 2 и Ь 2 соответственно. 35

Вычислительный процесс состоит из ïî<>ледовательности 1 шагов, заключающихся в передаче из,регистров 1 и 3 значений — — -!

g 2 и Ь 2 в соответствующие сумматоры-вычитатели 2 и 4 для сложения или вычитания из содержилюго этих сумматоров в соответствии со знаком Р . Так как

7 нормализованное число (делитель) по велиЧине л!еньше единицы, на первом шаге всегда P. = + 1. Одновременно с операцией,@ ! сложения (вычитания) в сумматорах на каждом шаге, в регистрах 1 и 3 производится сдвиг содержимого их только на один разряд lIQ каждом шаге для получения величи-!,,-1 ны а 2 и b,2, используе!.!ых на слэ у{! дуюшем шаге вычислен»!й.

Все шаги вычислений аналогичны, При Ь „ —— 1 процесс останавливается блоком управления, входы которого связаны с двул!я выходами сумматора-вычитателя 4, причем первый выход его — выход разряда, находящийся слева от двоичной запятой, и сигнал появляется при b . > 1

Ф

Второй выход элемента 4, представляющий собой группу !1 нулевых выходов триггеров дробной части сумматора-вьгчитателя 4, где

yl — количество разрядов в дробной части, через л1ноговходовой элемент И 6 связан со вторыл1 входом блока управления 5 . В случае, когда одновременно на входах блока управления 5 сигналы присутствуют, это соответствует досрочному окончанию вычислений (нри !! ).

По окончании вычислений результат— частное находится в сумматоре-вычитат ле 2.

Погрешность вычислений при разрядности и будет 5 6 Ъ2, что подтверждает высокую точность вычислений при высоком быстродействии (1< j !! ) и малых аппаратурных затратах.

Формула изобретения

Устройство для деления чисел, содержащее многовходовой элемент И, регистр делимого, выход которого соединен сс входом сумматора-вычитателя делимого, регистр делителя, выход которого соединен со входом сумматора-вычитателя делителя, о т» личающееся тем,что,сцелью упрощения устройства и повышения быстродействия, в него дополнительно введен блок управлепия, первый вход которого соединен с первым выходом сумматора-вычитателя делителя, вторые выходы которого через многовходовой элемент И соединены со вторым входом блока управления, выход которого подключен к управляющим входам всех сумматоров-вычнтателей и регистров, при этом установочные входы регистра делимого и сумматора-вычитателя делимого подключены к первой шине входного сигнала, а установочные входы регистра делителя и сумматора-вычитателя делителя подсоединены ко второй ш»ше входного сигнала.

5 11590

Дел

Составитель В. Соколов

Редактор О. С тенина Texpefl М. Левицкая KoppeKToð Л. Веселовская

Заказ 1318/1354 Тираж 864 П одпи сное

Ц1П!ИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская паб., д. 1/5

Филиал ППП "Патент", r Ужгород, ул. Проектная, 4