Аналоговое устройство для нормализации сигналов

Иллюстрации

Показать всеРеферат

О П И C A Н И Е,))),-,11!)н5

ИЗОБРЕ7ЕН ИЯ

Союз Совотскии

Социалистических е еспубпии

К АВТОРСКОМУ СВИДЕТЕЛЬСВ ВУ (61) Дополнительное к авт. саид-ву (22) Заявлено16.08.74 (21) 2053 е83У24 э (5l) M. KlI. Q 0е) 3; «3/t)t) с присоединением заявки № (23) Приоритет (43) Опубликовано 25.04,76Бюллетень № 1 5 (53) УДК В81 « - (08 8) (45) Дата опубликования описания

Государственный комитет

Совета Министров СССР

tEo делам изавретений и открытий (72) Автор изобретения

О. М. Саптыковский (71) Заявитель (54) ЛНА ЛОГОВОЕ УСТРОЙСТВО ДЛЯ НОРМА ЛИЗА1ЦФ1

СИГН)- «ЛОВ

Изобретение относится к кибернетике и может быть использовано при конструировании автоматов распознавания Временных функдий, работаюип«х в реальном м: штабе времени, например автоматов, распознавания радиолокационных и гидроакустических сигналов, выполненных на элементах аналоговой вы и)слительной техники.

Известно аналоговое устройство для нормализации сигналов, содержаепее линию задержки с отводами, подключен)еую входом ко входу устройства, а выходом сэединеиную со входом ч!!слителл блэка деления, аналоговую заноминаюеиую ячейку, фэрк«"рэ ватель стробимпульса, клю1«и.

11елью предлагаемого изобретения 11аляется пэвь.шение т3чнэсти работы (норма-111 зацин сиГн)iltr)B В trly Max), Эта пель достигается тем, что В устро11ство BBr.rt!.!«bt мнэговхэдэвэй сумматор, пэр1н-Оный -элемент и д )иолнитет!ьная л)«ния задержки, llэдключенная Вь)ходом кэ Входу формирователя стрэб)импульса и к перво,)у

Bxэду пэрвэгr3 клк)ч ), Второй Вход кэт:",)О).СОЕДИНЕН С ВЫХОДОМ .:Н )ГЭВХЭДЗВЭГЭ ЕУ, ..13тора, пэдключэннь)м ко входу порогового элемента, соединerlr«oro Выхэдом со входом дополнительной лиttt1и задержки, Bxэды мно

ГОВхэдэВОГО сумматора подключен!.1 с 33Т» ветственнэ к отводам линии задержки, ВыХЭД ПЕРВОГО КЛЮЧа СОЕДИНЕН СС ВХОДОМ аналэгDBÎH запоминаю)цей ячей:rt, Выход которой лодка)эчен ко входу зне)менателя блэка деления, сэединенногэ выходом с

1О первым входом второго ключа, второй вхэд которого подключен к выходу фэрмирователя стрэбимпульса.

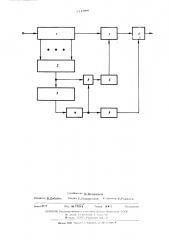

На чертеже дана блэк -с..хема эписневаеМОГО УСтРэйетва. ,к

1) r«:.7ýÃBBОе p ст()О11с твэ для r«)pMQ 71«l)÷nuu el!1 палов с 1де!)жит лин1«ю 1 -«адержки с 1! Отводами, к TBQQRM кэтэрэ1! пэд» к,ryl е» аналог< Bbtй сум матэр 2 на 11 ВхэдэВ. Выход су.,.1MBT3tpB 2 соединен с пэрэГЭВЫМ ЭЛЕМеитЭ ., ., ВЫХОД КотЭРОГЭ .Ет)Е)З !.полните-,7»tãK пи и - 4 зад р; пеи подключен к клк 1у 5, второй вход к торэг соединен с

В1.)ходок у; атэ1 3 2, а 1)1:.!XB.;l чер з ин-":13r ОВУ)3 ... )И3 АИ)17) )ПL Ю и !е))КУ .) СО ВХ

6116ОЗ

Это напряжение Я подается на вход знаменателя блока деления напряжений, на вход числителя которого приходит через интервал времени Т+ Д входной сигнал с линии 1 задержки. На выходе схемы деления формируются составляющие сигнала

X =Х /g Увеличение линии 1 задержки с на Д и введение линии задержки 4 необходимо для компенсации возможных разбросов формирования суммарного напряжениЙ g для сигналов данного класса.

Ключ 8 вместе с формирователем 9 осуществляет стробирование выхода блока жения. Вход числителя блока деления соединен с выходом линии 1 задержки, а выход — со входом ключа 8, второй вход которого подключен к выходу формирователя

9 стробимпульса, соединенного с выходом дополнительной линией 4 задержки.

На; линии 1 задержки поступает сигнал в смеси с шумом ХИ)+ 5 (й)

Полное время задержки линии 1 выбрано большим на величину h по сравнению с максимальной длительностью сигналов из заданных классов. На выходе сумматора 2 формируется напряжение, равное сумме составляющих сигнала Я=, X . Это наБ пряженпе сравнивается с порогом С и при )5 о

Я ) С ла выходе порогового элемента 3 о формируется сигнал, который пройдя линию

4 задержки через интервал Q открывает ключ 5, через который напряжение, равное S, с выхода сумматора 2 поступает ыа аналоговую запоминающую ячейку

6, где запоминается на время Т, равное максимальной длительности сигнала. деления напряжений только на интервале существования сигнала.

Введение в устройство схемь обнаружения с одновременной задержкой сигнала и запоминанием нормируюшего напряжения на время существования сигнала яозвопяет повысить точность нормали 1ции сигналов в шумах.

Формула изобретения

Аналоговое устройство для нормализации сигналов, содержащее линию задержки с отводами, подключенную входом ко

I входу устройства, а выходом соединенную со входом числителя блока деления, аналоговую запоминающую ячейку, формирователь стробимпульса и ключи, о т л ичающееся тем, что,сцельюповышения точности работы устройства, в него введены многовходовой сумматор, пороговый элемент и дополнительная линия задержки, подключенная выходом ко, входу формирователя стробимпульса и к первому входу первого ключа, второй вход которого соединен с выходом многовходового сумматора, подключенным ко входу порогового элемента, соединенного выходом со входом дополнительной линии задержки, входы многовходового сумматора подключены соответственно к отводам линии задержки, выход первого ключа соединен со входом аналоговой ячейки, выход которой подключен ко входу знаменателя блока деления, соединенного выходом с первым входом второго ключа, второй вход которого подключен к выходу формирователя стр об им пу льс а.

Из . ЛЬ йЫ

Заказ б1Г(Тираж Ы Й 1

Подписное

1\г1ИИПИ Государственного к >митвта Совета Министров СССР по двлам из< о1t. T ний и откр;. 1 и

Москва, 11»3: Раугнсная наб, 4

Филиал ППП "Патент", г. Ужгород, ул Г!рс с итиая, 4

В.Жовинский

Редактор В.Дибобес Техред Е (оГ1уру|нина ГГсрректор Е ронсновтз