Устройство для идентификации однократных временных сигналов

Иллюстрации

Показать всеРеферат

О П И С А H И Е (11) 511623

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено06. 05. 74 (21) 2023955««24 с присоединением заявки № (23) Приоритет

2 (51) М. Кл, С 01 Ь 1/00

Гасударственный комитет

Саввтв Министров СССР по делам изобретений и открытий (43) Опубликовано 25.04.7 Бюллетень М 15 (53) УДК881 3-33 (088.8 } (45) Дата опуоликования описания0,". 0.76 (72) Авторы изобретения

E. И. Кабанова и В. A. Махонин

Институт проблем передачи информации АН СССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИД 11Т, фИКАЦ14И ОДНОКРАТНЬ1

ВРЕМЕННЫХ СИГНАЛОВ

Из обретение отн осиная к вычислительн ой технике и может применяться для быстрой идентификации однократных времечных сигналов, представляемых суммой небольшого числа компонент, и, в частности, для Формантного анализа речи и для определения постоянных времени распада компонент радиоактивных смесей.

Известное устройство для идентификации однократных временных сигналов содержит оптимизаторь1, синхрогенератор, блок запсминания сигнала, подключенный выходом соответственно к первым входам управляемых измерителей параметров сигнала блок модели сигнала, выходом соединенный соответственно с первыми входами управляемь.х измерителей параметров модели, первую и вторую группу запоминающих ячеек.

Однако известное устройство требует боль-т шого числа пробных изменений настройки, что существенно снижает его быстродействие.

Цель изобретения — повышение быстродействия идентификатора сигналов, содержащих не орт ог ональны е к DMII оненты функции. 25

Это достигается тем, что первые входы оптимизаторов подключены к выходам соответствующих управляемых измерителей параметров сигнала, а вторые входы соединены, с выходами соответствующих управляемь1х измерителей параметрDB модели, выходы оптимизатDpDB через запоминающие ячейки первой групгы подключены ко входам соответствую щих запоминающих ячеек второй группы, к соответствующим входам управляемых измерителей параметров сигнала, к соответствующим входам управляемых измерителей параметров модели и к информационным «ходам блока модели сигнала, управляющий вход Ко торого соединен с одним выходом синхрогенератора, другие выходы которого подключены соответственно к управляющим входам блока зап оминания сигнала, оптимизаторов и запоминающих ячеек второй группы.

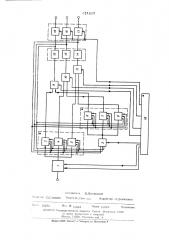

На чертеже приведена блок-схема устр ойства.

Предлагаемое устройство содержит блок

1 запоминания сигнала, блок 2 модели сигнала, управляемые измерители 3-8, оптимиза торы 9-1 1, запоминающие ячейки 1 2-14

511623 сэединены с измерителями, обладающими повыметров.

Изменения параметров настройки блока 5О

2 модели сигнала производятся поочередно, причем порядок осуществления этих изменений задан заранее и реализуется поочередным включением оптимизаторов 9, 10 и

11, посылками управляющих сигналов, этвэ-M димых от синхрогенератора.

Каждый оптимизатор, когда он включен, настраивает отдельпый параметр модели твк, первой группы, запоминающие ячейки 151 7 втор ой группы и синхр огенератор 1 8, Первая группа управляемых измерителей 3

4 и 5 измеряет параметры сигнапа, вторая

6, 7 и 8 измеряет параметры модели. Входы измерителей первой группы присоединены к выходу блока 1 запоминания сигнала, управляющие входы этого блока соединены с вых одами синхр огенерат ора, а инф ормационный вход - со входом устройства. I0

Вторая -группа управляемых измерителей состоит из измерителей 6, 7 и 8, входы которых присоединены к выходу блока 2 Мо лели сигнала, входы которого присоединены к выходам запоминающих ячеек параметров у модели 12, 13 и 14", к этим выходам под-. ключены также управляющие входы измерителей 3-8 и входы ячеек 15, 16 и 17 второй группы. Выходы однотипных измерителей из разных групп присоединены попарно 20 к входм, оптимизаторов настройки модели; выходы измерителей 3 и 6 ко входам оптимизатора 9, выходы измерителей 4 и 7 — ко входам оптимизатора 10, выходы измерите лей 5 и 8-ко входам оптимизатора 11, Вы-25 ходы оптимизаторов 9, 10 и 11 соединены со входами ячеек первой группы l, 13 и

l4. Выходы запоминающих ячеек 15, 16 и

17 (запоминания параметров) подключены к выходу устройства, а управляющие входы ЗО этих ячеек присоединены к выходу синхрогенератора 18.

Второй сигнал запоминается в блоке 1 под воздействием управляющего сигнала с первого выхода синхрогенератора 18, каж- З5 дая посылка управляющего сигнала со втс рого выхода синхрогенератора вызывает воспр оизв едение зап омненн ого сигнала, причем время воспро"зведения может отличаться от длительности записи, и, в частности, воспро-Ю изведение может быть значительно ускорено по сравнению с записью, Сдновременнэ с за пуском воспроизведения синхрогенератор включает блок модели сигнала 2, который генерирует сигнал, соетьетствующий значениям параметров, отводимых с выходов ячеек 12, 13 и 14, соединенных с входами модели источ ника сигнала, чтобы минимизироьать различия сигналов, поступающих на его вход от управляемых измерителей, Входы каждого оптимизатора щенной чувствительностью к изменениям параметра модели сигнала, управляемэг.с этим эптимизатэром, и понижейной чувс"вительнэстью к изм нениям лараметрэв, че управляемых этим эптимизатэрэм.

Этэ ослабляет влияние ошибок в нас-. -.— оойке одних параметров на оптимизацию настройки других, что сокращает продолжи= тельность поиска и тем повышает быстродействие устройства. Упр эщение устр эйства достигнуто тем, что вместо сложного многомерноГО oIITHvtIBGBTopG испэльз oBBHbl бэлс е простые одномерные оптимизаторы, .и тем „ что благодаря ускорению процесса самонаст-: ройки модели генератора сигнала вывод результатов поиска прэизвэдится после не-бОльшОГО числа циклoI - включений оптимиза.; торов = помощью последнего управляющего сигнала, которым синхрогенератор включает ячейки выходного блока запоминания параФ ормула из обретения

Устройство для: идентификации однократн:ыхх временных сигналов, содержащее опти-мизаторы, синхрэгенератор, блок запоми-нания сигнала. подключенный выходом cooT ветственно к первым входам управляемых измерителей параметров сигнала, блок модели сигнала, выходом соединенный соот ветственно с первыми входами управляемых измерителей параметров модели, первую и вторую группу запоминающих ячеек, о т л и ч а ю ш е е с я тем, что, с целью повьапепия бь-:стродейстьия, первые входи эптимизатopoI подкгпочены к выходам соответствующих управляемых измерителей параметров сигнала, а вторые входы соединены с выходами соответствующих управляемых измерителей параметров модели, вых оды оптим из ат ор ов через зап оминающие ячейки псрвой группы подключены ко входам соответствующих запоминающих ячеек второй группы, к соответствующим входам управляемых измерителей параметров сигна-.— ла, к соответствующим входам управляемых измерителей параметров модели и к инфор мациэнным входам блока модели сигнала, управ ляющий вход которого соединен с одним выходом синхрогенератора, другие выходы которого подключены соответственно к управляющим входам блока запоминания сигнала, оптимизаторов и запоминающих ячеек вт ор ой Гэуппы, 51%623

629G Изд. М 1З22 Тираж 1029

ЦНИИ! !11 Государственного комитета Совета Министров СССР ло делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Составит ел ь B.>ÊoâèícêHê

Редак:op G.Ñòåíèíà Текред М,Сем -с ° Корректор Л.Денискина