Буферный регистр

Иллюстрации

Показать всеРеферат

Союз Советсччх

Соции . ".стима",лин

Республик (11) 511631

К АВТОРСКОМУ СЗИДИПЛЬСТВУ (61) Дополнительное к авт. свид-s) (22) Заявлено 2.08 74.(21) 2056034/24 с присоединением заявки № (23) Приоритет (43) Огубликовано25.04.7S.Бюллетень И 15 (51) И. Кл.

Q 11 С 10/ОО

Государственный номнтет

Совета Инннстраа СССР по делам нзобратеннй

H DTKpblTNil (5Э) УДК 681,327.86 (088. 8) (45) Дата опубликования описания01.07,76 (72) Авторы изобретения

А, В. Шанин и В. И. Горин (71) Заявитель (54) БУФЕРНЫЙ РЕГИСТР

Изобретение относится к вычислительной технике.

Известные . буферные регистры, содержащие Щ триггеры, входы установки которых соединены с выходами одноименных цервьтх элементов И-НЕ, первые входы которых подключены к разрядным шинам, и ,второй многовходовой элемент И-НЕ, не достаточно надежны при приеме информации.

Белью изобретения является повышение . 1О надежности работы буферного регистра.

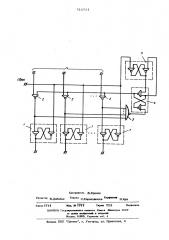

Поставленная цель достигается тем, что буферный регистр содержит триггеры блоки:ровки и задержки, вход установки которого соединен с шиной сброса, вход сброса и ин 15 вепсный > выход подключены соответственно к инверсному выходу и ко входу уста новки триггера блокировки, прямой выход которого соединен с шиной блокировки, а вход сброса через многовходовой элемент N И НЕ связан с установочными входами

RP триггеров.

На чертеже дана схема буферного регист.ра, который содержит Rg - триггер 1, элемент И НЕ 2, многовходовэй элемент 25

И-НЕ 3, триггер 4 блокировки, триггер

5 задержки. Исходное состояние устройствЭ:, триггеры задержки 5 и блокировки 4 нахо дятся в нулевом состоянии, на общей шине одноименных элементов 2 существует нулевой" потенциал; таким образом, RS триггеры 1 буферного регистра заблокярд вины. Работа начинается!с подачи сигнала по шине сброса, при этом RS триггеры

1 буферного регистра устанавливаются s нулевое состояние, а триггер 5 задержки ° в единичное" состояние.

Триггер 4 блокировки под воздействием нулевых сигналов на установочном я сбросном входах установится в состояние, когда на его прямом и инверсном выходах будут "единичные сигналы. Единичный сигнал с прямого выхода триггера 4 бло» кировки подготавливает одноименные эле» менты 2 для:приема данных, то есть RG ° триггеры 1 буферного ре истра деблокяру ются.

Прием информации буферным регистром в виде параллельного импульсного кода осуществляется через одноименные элемен.

51 1(31 ты 2. При этом импульсы отрицательной полярности с выхода одноименных элементов 2 устанавливают соответствующие

RS -триггеры 1 буферного регистра в

"единичное" состояние и одновременно по ступают на входы многовходового логического элемента 3.

"Единичный" сигнал на выходе много входового элемента 3 сформируется в момент появления первого информационного импульса и будет существовагь до момен ,та окончания импульса, имеющего максимальную задержку в линии связи. При этом на инверсном выходе т,тиггера 4 блокиров- ки установится "нулевой" потенциал, ко» 15 торый передним фронтом переключит триггер 5 задержки в "нулевое состояние.

Триггер 4 блокировки останется, в единичном состоянии до окончания последнего из пришедших информационных импульсов. ®

По окончании приема информации на выходе многовходового элемента 3 сформируется нулевой" сигнал, передний фронт которого установит триггер 4 блокировки в "нулевое" состояние, то есть произойдет блокировка Rg триггеров 1 буферного регистра до прихода следующего импульса

c6pocs.

Таким образом, буферный регистр отлича ется высокой надежностью приема информации, так как разброс вре,. ен лереключения

ЦЯ -триггеров не влияет :;а формирован, ;-. сигнала блокировки, при этом асинхронное . появления информационных импульсов, опре» деляемая различным временем задержек в цепях связи, компенсируется схемой блоки ровки. формула изобрете ния

Буферный регистр, содержаший RS триггеры, входы установки которых соединены с выходами одноименных первйх элементов И-HE „первые входы которых подключены к разрядным шинам, и второй многовходовой элемент И-НЕ, о т л ич а ю шийся тем, что, с целью повышения надежнпсти работы буферного регист ра, он содержит триггеры блокировки и задержки, вход установки которого соеди нен с шиной сброса, вход сброса и инверс ный выход подключены соответственно к инверсному выходу и ко входу установки триггера блокировки, прямой выход кото» рого соединен с шиной блокировки, s вход сброса через многовходовой элемент И

HE связан с установочными входамн

R 3 триггеров.

Састаавтелъ j3.фролов

Редактор ц тти,о е Теаред И арандашова рр H. äóê

Корреатор .Заказ 5ß4 иэд. м ЬЧМ Тараи 723 Подимсаое

I1HHHI1H I-осударспвеааого аоматета Соаета МааастРоа CCCP яо делам азобрепмвй в открытий

Москва„333635. Рауатскаа наб., 4 филиал ППП Патент, r. Ужгород, ул. Проектнвя, 4