Преобразователь напряжения в код поразрядного уравновешивания с переменным временем определения отдельных разрядов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ ())) ьц69з

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 14.06.71 (21) 1670177/26-21 с присоединением заявки № 1671638/26 21 (23) Приоритет

2 (51) М. Кл. H 03K 13 17

Государственный комитет

Соввта Министров СССР оо делам ивоорвтвннй и отирытий (43) Опубликовано 25.04 76.Бюллетень № 15 (53) УДК 681.325 (088.8) (45) Дата опубликования описания 18.08 76 (72) Авторы изобретения

А. Т. Пешков и Г. И. Сивицкий (71) Заявитель Белорусский ордена Трудового Красного Знамени государственный университет им, B. И. Ленина (54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД ПОРАЗРЯДНОГО

УРАВНОВЕШИВАНИЯ С ПЕРЕМЕННЫМ БРЕМЕНЕМ ОПРЕДЕЛЕНИЯ

ОТДЕЛЬНЫХ РАЗРЯДОВ

Изобретение относится к автоматике, вычислительной и измерительной технике.

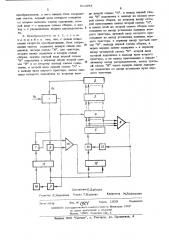

Известен преобразователь напряжения в код поразрядного уравновешивания, содержащий схему сравнения, преобразователь кода в напряжение, регистр кода, логический блок, распределитель и схему сборки.

Причем выход распределителя через логический блок, регистр кода, преобразователь кода в напряжение соединен с первьгм вхо- 1О дом сравнения, второй вход которой соединен с источником преобразуемого напряжения, а первый выход — с управляющим входом логического блока, вход которого подключен ко входу схемы сборки. 15

Однако известное устройство имеет ограниченную скорость преобразования, особенно при обеспечении высокоточного пре» образования.

Цель изобретения » сокращение времени рр преобразования.

Для этого в преобразователь введен блок сокращения тактов, первый вход которого соединен со вторым выходом схемы сравнения, второй вход - с выходом схе- 25 мы сборки, а выход — с уцраз;тяю:пил входом распределителя.

Кроме этого, для повышения скорости преобразования блок сокращен)*.г) тактов содержит первую линию задержки, четыре схемы И, два триггера, вторую л)пнгю задержки и вторую схему сборки. Причем лервый вход первой схемы "И" ггодключен к первому входу второй схемы И гг ко второму выходу схемы сравнения, а второй вход — к выходу нуля первого триггера, выход единицы которого подключен ко второму входу второй схемы И". Быход первой схемы "И присоединен к однолгу из входов второй схемы сборки, ко второму входу которой присоединен выход второй схемы И, а выход этой же второй схемы сборки подсоединен ко входу установки единицы второго триггера, единичный вход которого присоединен ко входу установки единицы первого триггера, к первому входу третьей схемы "И", выходу первой схемы сборки и через первую линию задержки к первому входу четвертой схемы "И, второй вход которой подключен к

511693

" -% !

,1.

Ря бы!

3

t

1

Ё I

YW—

5 т

Корректор МЛейзерман

Редактор Д.Народная Техред Т.Курилко и" " /я2 (Тираж 1029 Подписное

Заказ 5Я ф

ЦИИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, 113035, Раушская наб., 4

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 преобразования, в него введен блок сокращения тактов, первый вход которого соединен со вторым выходом схемы сравнении, вто рой вход — с выходом схемы сборки, а выход - с управляющим входом распределите ля, 2. Преобразователь по и. 1, о т л ичающийс я тем, что, спельюповыщения скорости преобразования, блок сокращения тактов содержит первую линию задержки, четыре схемы И, два триггера, вторую линию задержки и вторую схему сборки, причем первый вход первой схемы

"И подключен к первому входу второй схемы И и ко второму выходу схемы срав

15 нения, а второй вход первой схемы И"— к выходу нуля первого триггера, выход единицы которого подключен ко второму входу второй схемы И, а выход первой схемы И подключен к одному из входов второй схемы сборки, ко второму входу которой присоединен выход второй схемы И, а выход этой же второй схемы сборки подсоединен ко входу установки единицы второго триггера, нулевой вход которого присоединен ко входу установки единицы первого триггера, к первому входу третьей схемы И, выходу первой схемы сборки, и через первую линию задержки - к первому входу четвертой схемы И, второй вход которой подключен к выходу нуля второго триггера, а ее выход присоединен к управляющему входу распределителя, выход треть ей схемы И» через вторую линию задержки подключен ко входу установки нуля первого триггера.