Дифференцирующе-сглаживающий преобрахователь частотно- импульсных сигналов в код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 5|,248C} (61) Дополнительное к авт. саид-ву(22) Заявлено 05.07. 74 (21) 2044386/18 24 с присоединением заявки №(23) Приоритет(43) Опубликовано30.04. 76.Бюллетень №16 (45) Дата опубликования описания 30.06.77 (51) М. Кл.е 06,Т 3/00

Гооудеротвенный комитет

Совете Ииниотров СССР оо делам изобретений и открытий (53) УДК 681.34 (0SS.8 ) (72) Автор . изобретения

H. И. Холкин

Рязанский радиотехнический институт (71) Заявитель (54) ЛИ ФФЕРЕНЦИРУЮЩЕСГЛА?КИВАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ

ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ В КОД

Изобретение относится к области автоматики и вычислительной техники и может быть использовано, в частности, как усч ройство, сопрягающее частотные датчики с цифровой вычислительной машиной в системах регулирования и управления, а также как автономное цифровое измерительное устройство.

Известны цифференцирующе-сглаживающие преобразователи частотно-импульсных 10 сигналов в код, содержащие блок разделения совпадающих импульсов, первый вход которого подключен к входу преобразователя, а выходы через последовательно соединенные первый распределитель импульсов и тб вычитающий блок подключены к сигнальным входам второго распределителя импульсов и входам первого реверсивного счетчика, выходы разрядов которого соединены соответственно с входами первого двоичного 20 умножителя, входом пеового знакового триггера, подключенного выходами к управляющим входам распределителей импульсов, и первыми входами сумматора, вторые входы которого соединены с разрядными выхода- 25 ми второго реверсивного счетчика, подключенного выходами к входам второго двоичного умножителя и входу второго знакового триггера, выходы которого соединены с управляющими входами второго распределители импульсов, подключенного сигнальным входом к выходу второго двоичного умножителя.

Недостатком таких преобразователей является динамическая ошибка по ускорению при измерении сигнала и его скорости изменения.

11елью изобретения является расширение динамического диапазона работы преобразователя и повышение точности.

Это достигается тем, что в преобразователь введены дополнительные распределитель импульсов, реверсивный счетчик и двоичный умножитель, соединенный выходом со вторым входом блока разделения совпадающих импульсов, а входами подключенный к выходам разрядов дополнительного реверсивного счетчика, входы которого соединены с выходами второго распределителя импульсов, причем выход первэгэ дв ичнэгэ

">1248Î множителя соединен с сигнальным входом второго распределителя импульсов и входом дополнительного распределителя импульсов, подключенного выходами к входам второго реверсивного счетчика и соединенного управляющими входами с выходами знаковых триггеров.

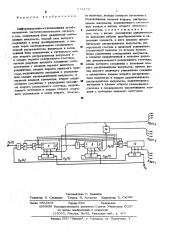

На чертеже изображена блок-схема предлагаемого преобразователя.

Преобразователь содержит блок 1 разделения совпадающих импульсов, распределитель 2 импульсов, вычитающий блох 3, реверсивный счетчик 4 со знаковым триг гером 5 и двоичным умножителем 6, рас- . пределитель 7 импульсов, реверсивный счет-45 чик 8 со знаковым триггером 9 и двоичным умножителем 10, распределитель 11 импуль

cob, реверсивный счетчик 12, двоичный ум ножитель 13 и сумматор 14.

Вход F„ (4 ) преобразователя через блок 1 разделения совпадающих импульсов, распределитель 2 и вычитающий блок 3 соединен с суммирующим входом реверсивного счетчика 4 и через распределитзль

11 — с реверсивным счетчиком 12. Зычитающий вход реверсивного счетчика 4 через вычитающий блок 3, распределитель 2 и блок 1 разделения соединен с выходом двоичного умножителя 13,, а также через распределитель 11 - с входом реверсивно-

ЭО го счетчика 12. Выходы двоичных умножителей 6 и 10 соединены через распредели тель 11 со счетчиком 12. Выход умножителя 6 через распределитель 7 соединен со счетчиком 8. Выход N

ВЬ(х З счетчика 4 служит для измерения ускорения сигнала

Г, (t ). Сумма сигналов с выходов счетчиков 4 и 8, образующаяся в сумматоре 14, служит для измерения скорости сигнала

Р„(4 ), выход М „. счетчика 12

Ю

ВЬ(X предназначен для измерения сигнала F (). х

Преобразователь работает следующим образом.

Измеряемая частота поступает через блок 1, распределитель 2 и вычитающий

45 блок 3 на входы реверсивных счетчиков 4 и 12.

При атом значения выходов преобразователя описываются выражениями

4 (ь(<) о Bb(X

ablX

, () = . .,„) х (М, 3 т ю(1) = V, Н,(a), где,„, y) p - число разрядов в сче1 чиках 12, 8, 4, Bb)X,Ô> г® "ВЬ () кущие значения чисел в счетчиках 12, 8,.

4, npep,".òàâëåaíûå в прямом коде с фиксированной запятой;

Й B (4) — сумма значений счет»

3))Х, чиков ч и 8, которая может вычисляться в сумматоре 14, представляет несмещенную сглаженную оценку скорости изменейИФ частоты.

Уравнения (1) в онераторной форме имеют вид

) х(Р) " " (") Р7 Lò р) "ВЬ)Х ® зь(х ® 2Ф аь(х (Р) () F xp) вьи ®= p (p - вь)х Ф Bb)x lP)+ Ф

P о ((з

1 у 1 2- у 9 э 7 о о о

Значение И„,„,М, М„Ь)х, (Р) N . (P),.ÿâëÿþøèeñÿ корнями сивых стемы уравнений (2), имеют вид

7x(p) 1+ p +Р Та, Г . ), .РТ +Р „,+Р > V х(Р) 1+ pTq

2 - . «, П,рот т, т.т т ® Р

)р) p2,гх (Р) ) то +Р ;+Р +P y.,.g М

Наличие оператора Р в выражении (5) указывает на возможность использования значения М,„ (t ) для оценки второй

3 производной сигнала PÄ (4 ), равенство первых трех и первых двух коэффициентов в числителе и знаменателе выражений (3) и (4) указывает на отсутствие частоты и ее первой производной.

Формула изобретения ди ференцируюше-сглаживающий реобпазователь частотно-импульсных сигналов в код, содержаший блок разделения совна—

: дающих импульсов, первый вход которого

1 подключен к входу преобразователя, а выходы через последовательно соединенные первый распределитель импульсов и вычи10 таюший блок подключены к сигнальным входам второго распределителя импульсов и и входам первого реверсивного счетчика, выходы разрядов которого соединены соот ветственно с входами первого двоичного 15 умножителя, входом первого знакового триггера,.подключенного выходами к управляютаим входам распределителей импульсов, и первыми входами сумматора, вторые входы которого соединены с разрядными выходи- 9 ми второго реверсивного счетчика, подключенного выходамн к входам второго двоич ного умножителя и входу второгс, знакового триггера, выходы которого соединены с управляющими входами второго распределителя импульсов, подключенного сигнальным входом к выходу второго двончного умножителя, о т л и ч а ю ш и и с я тем, что, с пелью расширения динамического диапазона работы преобразователя и повышения точности, в него введены дополнительные распределитель импульсов, реверсивный счетчик и двоичный умножитель, соединенный выходом со вторым входом блока разделения совпадающих импульсов, а входами подключенный к выходам разрядов дополнительного реверсивного счетчика, входы которого соединены с выходами второго распределителя импульсов, причем. выход первого двоичного умножителя соединен с сигнальным входом второго распредели» теля импульсов и входом дополнительного распределителя импульсов, подключенного выходами к входам второго реверсивного счетчика и соединенного управляющими входами с выходами знаковых триггеров.

Составитель С. Казинов

Редактор Н. Суханова Техред И. Асталош Корректор E. Скучка

Заказ 956/508 Тираж 864 По дпис ное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

11ЗО35, Москва, Ж-35, Раушская наб., p. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4