Двухтактный усилитель

Иллюстрации

Показать всеРеферат

(111 5I2556

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со1оз Советских

Социалистических

Реопублик (61) Дополнительное к авт, свид-ву (22) Заявлено 02.07.73 (21) 1937092/09 с присоединением заявки № (23) Приоритет

Опубликовано 30.04.76. Бюллетень ¹ 16

Дата опубликования описания 17.06.76 (51) М. Кт а Н 03F 3/26

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.375.4:621. ,375.127(088.8) (72) Автор изобретения

В, И. Белянкин (71) Заявитель (54) ДВУХТАКТНЫЙ УСИЛИТЕЛЬ

Изобретение относится к радиотехнике и может применяться в системах автоматического регулирования с использованием широтно-импульсной модуляции.

Известен двухтактный усилитель, содержащий последовательно соединенные относительно источника питания силовые транзисторы.

Однако эти усилители не устраняют сквозные токи при работе силовых транзисторов в режиме насыщения.

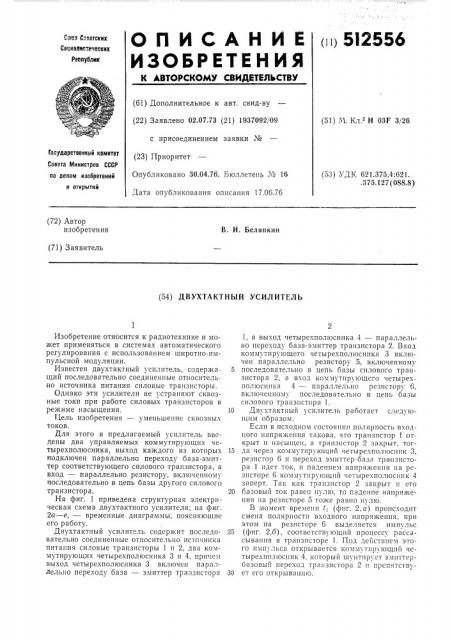

Цель изобретения — уменьшение сквозных токов, Для этого в предлагаемый усилитель введены два управляемых коммутирующих четырехполюсника, выход каждого из которых подключен параллельно переходу база-эмиттер соответствующего силового транзистора, а вход — параллельно резистору, включенному последовательно в цепь базы другого силового транзистора.

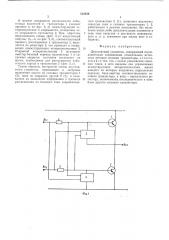

На фиг. 1 приведена структурная электрическая схема двухтактного усилителя; на фиг.

2а — е, — временные диаграммы, поясняющие

его работу.

Двухтактный усилитель содержит последовательно соединенные относительно источника питания силовые транзисторы 1 и 2, два коммутирующих четырехполюсника 3 и 4, причем выход четырехполюсника 3 включен параллельно переходу база — эмиттер тра:.1зисторг

1, а выход четырехполюсника 4 — параллельно переходу база-эмиттер транзистора 2. Вход коммутиру!ощеГО четы11ехпол10снпка 3 включен параллельно резистору 5, включенному

5 последовательно в цепь базы силового транзистора 2, а вход коммутирующего четыпехпогпосника 4 — параллельно резистору 6, включенному последовательно в цепь оазы силОВОГО транзистора 1.

10 Двухтактный усилитель работает следу1ощим образом.

Если в исходном состоянии полярность входного напряжения такова, что транзистор 1 открыт и насыщен, а транзистор 2 закрыт, тог15 да через коммутирующий четырехполюсгп1к 3, резистор 6 и переход эмиттер-база транзистора 1 идет ток, и падением напряжения на резисторе 6 коммутирующий четырехполюсннк 4 заперт. Так как транзистор 2 закрыт и его

20 базовьш ток равен нулю, то падение напряхкения на резисторе 5 тоже равно нулю.

В момент времени fi (фиг. 2, а) происходит смена полярности входного напряжения, при этом на резисторе 6 выделяется импульс

25 (фиг. 2,б), соответствующий процессу рассасывания в транзисторе 1, Под действием этого импульса открывается коммутирующий четырехполюсник 4, который шунтнрует эмиттербазовый переход транзистора 2 и прсп11тств 30 ет его открываншо, 51255Е

Фиг.1

В момент завершения рассасывания избыточных носителей в транзисторе 1 (момент времени tq на фиг. 2, в) коммутирующий четырехполюсник 3 закрывается, вследствие чего открывается транзистор 2. При обратном переключении схемы (фиг. 2,г) аналогичный импульс (t3 — t4 на фиг. 2, д), соответствующий процессу рассасывания в транзисторе 2, выделяется на резисторе 5, что приводит к открыванию коммутирующего четырехполюсника 3.

Открытый четырех пол юсник 3 шунтирует эмиттер-базовый переход транзистора 1 и сохраняет закрытое состояние последнего па время, необходимое для рассасывания избыто шого заряда в транзисторе 2 (фиг. 2, е).

Таким образом, построение схемы двухтактного усилителя, приводящее к задержке включения одного из силовых транзисторов 1 (2), пока пе закрылся другой 2 (1), и основанное на выделении информации о процессе рассасывания из базового тока закрывающегося транзистора 2 (1), позволяет исключить сквозные токи в силовых транзисторах 1, 2, работающих в режиме насыщения, без включения каких-либо дополнительных элементов в

5 цепь тока нагрузки и достигнуть максимального к. п. д. усилителя при малом весе и габаритах.

Формула изобретения

Двухтактный усилитель, содержащий последовательно соединенные относительно источника питания силовые транзисторы, отличаю шийся тем, что, с целью уменьшения сквоз15 ных токов, в него введены два управляемых коммутирующих четырехполюсника, выход каждого из которых подключен параллельно переходу база-эмиттер соответствующего силового транзистора, а вход — параллельно ре20 зистору, включенному последовательно в цепь базы другого силового транзистора.

512556 c

Составитель И. Черняк

Техред E. Подурушииа

Редактор Т. Рыбалова

Корректор А. Галахова

Типография, пр. Сапунова, 2

Заказ 1310 12 Изд. № 1329 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5