Двухканальный дешифратор

Иллюстрации

Показать всеРеферат

пц 5I2575

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву (22) Заявлено 15.11.74 (21) 2075282/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.04.76. Бюллетень № 16

Дата опубликования описания 16.06.76 (5! ) М. 1(л,е Н ОЗК 13, 24

Государственный комитет

Совета Министров СССР (53) $ Ä 1(681.32 5.63 (088.8) по делам изобретений и открытий (72) Авторы изобретения В. А. Иванов, В. В. Прушинский, А. С. Савлук, А. Г. Филиппов и A. Н. Чистяков (71) Заявитель (54) ДВУХКАНАЛЬНЫЙ ДЕШИФРАТОР

Изобретение относится к области вычислительной техники и предназначено для использования в качестве одного из элементов управления матрицей памяти интегрального оперативного запоминающего устройства.

Известны двухканальные дешифраторы, содержащие в каждом из двух каналов входной транзистор, база которого через резистор соединена с положительной шиной источника питания, эмиттер подключен к входной шине, а коллектор — к базе переключающего транзистора, коллектор которого соединен с анодом диода и через резистор с положительной шиной источника питания, а эмиттер — с базой первого инвертирующего транзистора и через резистор с отрицательной шиной источника питания, к которой также подключен эмиттер и через резистор база второго инвертирующего транзистора.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения — повышение быстродействия.

Цель достигается тем, что в каждый из двух каналов дешифратора введены первый и второй дополнительные инвертирующие транзисторы, эмиттеры которых подключены к эмиттерам, а коллекторы — к коллекторам соответствующих инвертирующих транзисторов, причем база первого дополнительного инвертирующего транзистора первого канала подключена к базе первого инвертирующего тразистора второго канала, база первого дополнительного инвертирующего транзистора

5 второго канала — к базе второго инвертирующего транзистора первого канала, база второго инвертирующего транзистора второго канала — к базе второго дополнительного инвертирующего транзистора первого канала, 10 база первого инвергирующего гранзистора первого канала — к базе второго дополнительного инвертирующего транзистора второго канала, а катоды диодов первого и второго каналов подключены соответственно к ба15 зам вторых инвертпрующих транзисторов.

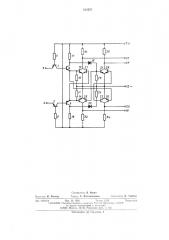

На чертеже представлена принципиальная схема двухканального дешифратора.

Он содержит входные транзисторы 1 и 2, эмиттеры каждого из которых являются вхо20,дами дешифратора 3 и 4, базы через резисторы 5 и б подключены к положительной шине 7, а коллекторы — к базам соответствующих переключающих транзисторов 8 и 9. Эмиттсры транзисторов 8 и 9 подключены соответствен25 но через резисторы 10 и 11 к отрицательной шине 12 и к базам выходных инвертирующих транзисторов 13 и 14, коллекторы которых служат выходами дешифратора 15 и 16. 1(оллекторы транзисторов 8 и 9 соответственно

30 подсоединены черсз резисторы 17 и 18 и по5

3 ложительной шине 7, а через диоды 19 и 20 к базам вторых инвертирующих транзисторов

21 и 22, базы которых соответственно через резисторы 23 и 24, а эмиттеры непосредственно, подключены к отрицательной шине 12; коллекторы транзисторов 21 и 22 являются выходами дешифратора 25 и 26. Коллекторы и эмиттеры дополнительных инвертирующих транзисторов 27, 28, 29 и 30 подключены соответственно к коллекторам и эмиттерам транзисторов 13, 14, 21 и 22, а базы транзисторов 27, 28, 29 и 30 соединены соответственно с базами транзисторов 14, 21, 22 и 13.

Между выходами дешифратора 15, 16, 25 и

26 и положительной шиной 7 включены нагрузочные резисторы 31, 32, 33 и 34.

Двухканальный дешифратор работает следующим образом.

Ко входам 3 и 4 приложен высокий уровень потенциала. Током через резистор 5 открывается транзистор 8 и суммарным током через резисторы 5 и 17 — транзисторы 13 и

30. Аналогично током через резисторы 6 и 18 второго канала открываются транзисторы 14 и 27. Транзисторы 21, 22, 28 и 29 в этом случае закрыты, так как напряжение на коллекторах насыщенных транзисторов 8 и 9 составляет Uq,— . У„„и его недостаточно для открывания через диоды смещения 19 и 20 инвертирующих транзисторов 21, 22, 28 и 29. Поэтому на выходах 15, 16 и 26 устанавливается низкий, а на выходе 25 — высокий уровень потенциала.

Если на один из входов, например, на вход

3, подать низкий уровень потенциала, то коллекторным током транзистора 1 закрывается транзистор 8 и инвертирующие транзисторы 13 и 30, а ток, протекающий через резистор 17 и диод 19 поступает в базы транзисторов 21 и

28, вызывая их насыщение. Прп данном сочетании сигналов на входах 3 и 4 на выходах 15, 16 и 25 окажется низкий, а на выходе 26— высокий уровень потенциала. При любых комбинациях сигналов на входах только на одном выходе будет высокий уровень потенциала, и при выборе одной схемы из четырех необходим один логический вход в управляемой схеме. При применении дешифратора без промежуточной дешифрации на двух из его четырех входов будет высокий, а на двух дру12575 гих — низкий уровень потенциала, и в каждой управляемой схеме необходимо иметь два логических входа. При применении двух дешифраторов для дешифрации шестнадцати схем в первом случае в каждой схеме должно быть два, а во втором — четыре логически входа в каждой дешифрируемой схеме. Т. е. применение дешифраторов с промежуточной дешифрацией позволяет вдвое уменьшить количество логических входов дешифрируемых схем.

Формула изобретения

30

50

Двухканальный дешифратор, содержащий в каждом из двух каналов входной транзистор, база которого через резистор соединена с положительной шиной источника питания, эмиттер подключен к входной шине, а коллектор— к базе переключающего транзистора, коллекгор которого соединен с анодом диода и через резистор с положительной шиной источника питания, а эмиттер — с базой первого инвертирующего транзистора и через резистор с отрицательной шиной источника питания, к которой также подключен эмиттер и через резистор база второго инвертирующего транзистора, отличающийся тем, что, с целью повышения быстродействия, в каждый из двух каналов дешифратора введены первый и второй дополнительные инвертирующие транзисторы, эмиттеры которых подключены к эмиттерам, а коллекторы — к коллекторам соответствующих инвертирующих транзисторов, причем база первого дополнительного инвертирующего транзистора первого канала подключена к базе первого инвертирующего транзистора второго канала, база первого дополнительного инвертирующего транзистора второго канала — к базе второго инвертирующего транзистора первого канала, база второго инвертирующсго транзистора второго канала — к базе второго дополнительного инвертирующего транзистора первого канала, база первого инвертирующего транзистора первого канала — к базе второго дополнительного инвертирующего транзистора второго канала, а катоды диодов первого и второго каналов подключены соответственно к базам вторых инвертирующих транзисторов, 512575

Кор1 сктор О. Т орнна

Редактор Н. Коляда

Зак 1219/14 Изд. ¹ 1286 Т: рвгк 1020 Подл:,свое .Ц111ИПИ Государственного комитета Сиеста Мпi.::ñòðñ.; СССР по делам изобретений и от:;p .,tòèè

113035, Москва, )1(-35, Раун скан наб, д. 4:5

Типография, пр. Сапунова. 2

Составптевь Л, Вагян

Текред Л. Камышникова

2б

/б