Устройство для исправления ошибок в информации, закодированной циклическим кодом

Иллюстрации

Показать всеРеферат

ОЛИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советакик

Социэлистическик

Республик

5I2 589 (61) Дополнитслш1ое к авт. си!д-ву— (22) Заявлено 04.04.74 (21) 2011917/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 30.04.76. Бюллетень № 16

Дата опубликования описания 27.01.77 (51) М. Кл.2 Н 041 1/10

G 06Г 11/10

Государственный комите1

Совета а1инистроа СССР аа делам изобретений и открытий (53) УДК 681.326.75 (088.8) (72) Авторы изобретсшгя В. С. Толстяков, В. Н. Номоконов, Д. О. Яковлев и В. И. Соболевский (71) Заявитель

Ленинградский ордена Ленина электротехнический институт имени В. И. Ульянова (Ленина) (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

В ИНФОРМАЦИИ, ЗАКОДИРОВАННОЙ ЦИКЛИЧЕСКИМ

КОДОМ

Изобретение относится к области обраоотки сложных сигналов, в частности к реализации помехоустойчивого кодирования, п монист быть использовано в системах передачи цифровой информации.

Известно устройство для исправления ошибок в информации, закодированной ш:клнчсским кодом, содержащее регистр сдвига, выходы разрядов которого подключены к Входам блока сумматоров по модулю два, ме коритарный элемент, входы которого соединены с выходами блока сумматоров по модул;о два, а выход — с входами двухвходовых сумматоров по модулю два, включенных между соответствующими разрядами регистра сдвига.

Однако в таком устройстве доля реально исправляемых ошибок кратности, превышающей кратность гарантированно исправляемых ошибок, относительно невелика, что дела т недостаточнои вероятность правильного декодирования в условияY сильных помех. Это связано с тем, что весь процесс декодирования осуществляется при неизменной системе Ipoве.рок.

Цель изобретения — повышение эффекгивности устройства для мажоритарного декодирования циклических кодов, выражающееся в увеличении доли исправляемых ошибок и в соответствующем повышсн1ш вероятности правн1ьного декодирования.

;-.!то достигается тем, что в устройство введен коммутатор, выходы которого соединены с входамн установки нуля соответствующих разрядов регистра сдвига.

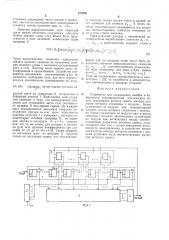

На фиг. 1 пзооражена структурная схема устройства для нсправле1п!я ошибок в ннфорз121\ "Iн1 закоднрованн01! цн1"лнческнм кодох1, II2 фиг. 2 — схема устройства для кода (15; 4).

Устройство содержит и-разрядный сдвнг3Iощнн pcI IIOT11 1, мсжд! разпядаз!11 которого имеются дополнительно встроеьч ые двухвходовые сумматоры 2 по модулю два, олок 3 сумматоров по модулю два, мажоритарный элемент 4 н коммутатор 5 с к — 1 выходамн.

Выходы разрядов рсI истр3 вхОдами блока 3 сумматоров по модулю два, которьш строится в соответствии с системой npoBP11O1i кода. Выходь! 0;IOIi3 C AIXIBTOpOB ключе!ниI к входам мажоритарного элемента 4, выход которого соединяется с вторыми Bxoz2мн встроенных сумматоров 2. Вход коммутатора 5 связан с шиной Т„начала декодирования, а его выходы — с входамп установки нуля определенных разрядов регистра так, что

3-й выход коммутатора подключен к входу

R разрядов с номерами 1, для которых в поЗО рождающем по11111oме

512589

«0»

3,14

4,1

6,!З

8,2

9,7

10,5

11,12

«!»

«2»

«3»

5,2

7,1 4

9,3

10,8

1 1,6

12,13

6,3

10,4

1 1,9

12,7

13,14

7,4

1 1,5

12,10

13,8

10 (2) 15

«0»

«1»

«2»

«з»

3,14

4,1

6,13

8,2

9,7

10,5

11,!2

5,2

7,14

9,3

1О,8

1 1,6

12,13

6,3

1 1,9

12,7 ! 3,14

7

li

12

1З

131

«9» «8» «7»

1 О

1 О 1 о о о

«6» «5» «4» «3» «2»

O ! 0 о ! o o о о о о о

«1» «О»

О 1

1 О

О О о о

65

g(х) др+ gi «+я2х ...+g„— /с хкоэффициенты д; с номерами от () до ((— !г-l-s+2) равны нулю. На фиг. 1 не показаны цепи тактовых и синхронизирующих сигналов, а также ключи, используемые обычно в декодерах циклических кодов и не имеющие существенного значения для рассмотрения принципа работы предлагаемого устройства.

Работает устройство следующим образом.

После ввода кодового слова ар, аь а2 ... а n IB регистр 1 сигналы с выходов разрядов регистра поступают на сумматоры блока 3, на выходах которых вырабатываются значения начального символа ар в соответствии с системой проверок кода. В соответствии с большинством совпадающих результатов проверок мажоритарный элемент 4 принимает решение об оценке значения ар, которое является правильным, если в кодовом слове ошибки отсутствовали или если имелась корректируемая комбинация (конфигурация) ошибок. Сигнал с выхода мажоритарного элемента поступает на выход устройства, а также по цепи обратной связи — на входы сумматоров 2. Так что при следующем тактовом импульсе сдвига в разряд регистра, перед которым включен сумматор, будет записан результат суммирования по модулю два сигнала с предыдущего разряда и сигнала обратной связи. После сдвига содержимого регистра 1 и до выработки значения следующего информационного символа с коммутатора 5 подается импульс, устанавливающий в нуль те разряды регистра, которые пе являются необходимыми для декодирования следующих символов. Таким образом происходит фактическое отключение некоторых разрядов, регистра от блока сумматоров, в резултате чего возможные ошибки в этих разрядах не влияют более на итог декодирования. Тем самым обеспечивается изменение системы проверок в сторону повышения их достоверности в процессе декоди!рования

В течение k тактов декодирования сигнал из канала связи в регистр не подается, что эк. вивалентпо подаче комбинации 00...0.

Поясним сказанное на примере декодирования кода (15; 4), имеющего полином

g(x) =х" +х р+х +х +х +х +х +1 и соот ветственно и (х) =х4+х+1. Порождающая матрица этого кода имеет вид

«14» «13» «12» «11» «10» о о о о о о о

Непосредственно из этой матрицы следует система разделенных проверок для первых четырех символов кода ар, а!, а, аз (в первой строке каждого столбца записан номер информационного символа а;, а в следующих строзо

55 ках под ним указаны номера символов, входящих в проверки для а; ).

В результате видоизменения цепи обратной связи и последовательного исключения определенных символов кода указанная система проверок приобретает вид

Структурная схема устройства для кода (15; 4) приведена на фиг. 2. Здесь дополнительные сумматоры по модулю два включены после разрядов регистра с номерами «11», «10», «9», «8», «6», «4», «3». Для реализации системы проверок (3) требуется после декодирования символа а, записать «О» на позицию символа а4, а после декодирования a> — «О» на позиции символов а;, ар и а!р. Это дости. гается подк;почением первого и второго выходов и коммутатора соответственно к входам установки «О» разрядов регистра с номерами

2 и 2, 5, 7. После декодирования ар на начальном шаге декодирования должен быть обнулен нулевой .разряд регистра, однако в предлагаемом устройстве это оказывается излишним, поскольку значение символа, записанного в нулевом разряде, не используется на последующих шагах декодирования.

Предлагаемый декодер исправляет ряд комбинаций ошибок кратности 1=4, которые не исправляются в известном устройстве. К таким комбинациям относится, например, искажение символов а4, а, ар и а!4. В то же время, все ошибки этой кратности, исправляемые в известном устройстве, исправляются также и в предлагаемом устройстве.

Известно, что наиболее достоверными проверками являются проверки с одним членом в правой части вида а; =а, Поэтому увеличение числа таких проверок в процессе декодирования повышает достоверность результата.

В общем случае декодирования циклических кодов, когда исходные проверки имеют более двух членов в правой части, происходит но512589

, 0 (4) степенное сокращение числа членов в проверках, так что на последнем шаге декодирования остаются только проверки вида а; =а

Действие видоизмененной цепи обратной связи можно объяснить следующим образом.

Любое кодовое слово v(x) может быть представлено в виде линейной комбинации строк матрицы 6

Такое представление позволяет однозначно связать наличие единицы на начальной позиции кодового слова с наличием составляющей

g (x) в v (x). Поэтому после первого шага декодирования в предлагаемом устройстве проводится исключение составляющей g (x) из принятого сообщения v(x), для чего осуществляется посимвольное суммирование по модулю два u< )p((i путем подачи сигнала ооI ратной связи на сумматоры 2, встроенные в буферный регистр 1. Выполнение этой операции приводит к тому, что порождающей матрицей для оставшейся части v (x) оказывается матрица 6 без первой строки. На каждом шаге декодирования описанная операция повторяется, причем íà s-м шаге обнуляются разряды регистра 1 с номерами г, которым соответствуют столбцы матрицы 6, не имеющие единиц в последних Й вЂ” ь — 1-х строках, или, что то же самое, для которых в поличоме g(x) есть нулевые коэффициенты при степенях от (i) до (г — А+в+2). Таким образом, на последнем шаге от матрицы 6 остается только ее последняя строка, что обусловливает палич ге только одного члена в правой части проверок для символа а,. К этому моменту отключенными оказываются все разряды, соответствующие символам, имеющим нули в этой строке матрицы.

Предлагаемый декодер с повышенной достоверностью вырабатывает значения а, а, ... а, в представлении кодового слова в форме (4), по которым легко могут быть on15 ределены значения информационных символов а,, а,,..., а,, г соответствующих разделенному коду (например, для кода (15,4) имеем и<) гг! гг г o2 g H сгЗггг ио ) °

Если же кодирование осуществляется в соогветствии с (2), то надобность в дополнительных преоперациях в декодере отпадает.

Формула изобретения

25 Устройство для исправления ошибок в информации, закодированной циклическим кодом, содержащее регистр сдвига, выходы разрядов которого соединены с входами блока сумматоров по модулю два, мажоритарный зр элемент, входы которого соединены с выходами блока сумматоров по модулю два, а выход соединен с входами двухвходовых сумматоров по модулю два, включенных между соответствующими разрядами регистра сдвига, or ãèЗ5 чаюигееся тем, что, с целью повышения досговерности декодирования, в устройство введен коммутатор, выходы которого соединены с входами установки нуля соответствующих разрядов регистра сдвига.

512589

Фиг. 2

Составитель В. Крылова

Редактор М. Грузова Техред А. Камышникова,Корректор Л. Брахннна

Заказ 5199 Изд. № 1370 Тираж 864 цНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Подписное

N0T, Загорский филиал