Устройство выделения рекуррентного синхросигнала с исправлением ошибок

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ())) 5)259! изоы етеиия

С юэ Соаатскик

Социалистических

Республик г

К АВТОРСКОМУ С.ВИ.- :-;ЫайЬ(..18

l ,( — -: --:1 (51) М. Кл Н 04). 7/0 (61) Дополнительное к авт. свид-ву (22) Заявлено 02.04.73 (21) 1900884/09 с Я л у с присоединением заявки No (23) Приоритет

Опубликовано 30.04.76. Бюллетень No 16

Дата опубликования описания 16.06.76

Гаоударстввнный комитат

Саввта Министров СССР по лалом нзобратаиий и открытий (53) УДК 621.394(088.8) (72) Автор изобретения

И, Ф. Хомич

Пензенский завод-ВТУЗ (Филиал Пензенского политехнического института) (71) Заявитель (54) УСТРОЙСТВО ВЫДЕЛЕНИЯ РЕКУРРЕНТНОГО

СИНХРОСИГНАЛА С ИСПРАВЛЕНИЕМ ОШИБОК

Изобретение относится к электросвязи, в частности к устройствам синхронизации, и может использоваться для помехоустойчивого выделения сигналов фазового пуска в аппаратуре передачи двоичной информации.

Известно устройство выделения рекуррентного синхросигнала с исправлением ошибок, содержащее объединенные по входу две цепи, одна из которых состоит из последовательно соединенных приемного блока и формирователя, а вторая — из последовательно соединенных блока обработки сигналов, элемента

«НЕТ» и счетчика совпадений, при этом между выходов приемного блока и выходом формирователя включена схема сравнения.

Однако известное устройство обладает недостаточно высокой точностью выделения синхросигналов, так как решение об исправлении каждого принимаемого знака основывается лишь на однократной его проверке на соответствие,рекуррентному закону.

Цель изобретения — повышение точности выделения синхросигналов.

Для этого между выходами схемы сравнения и формирователя включены последовательно соединенные решающий блок, переключатель, управляющий вход которого соединен с выходом блока обработки сигналов, и блок исправления ошибок, причем выход переключателя соединен с входами сброса решающего блока и элемента «НЕТ».

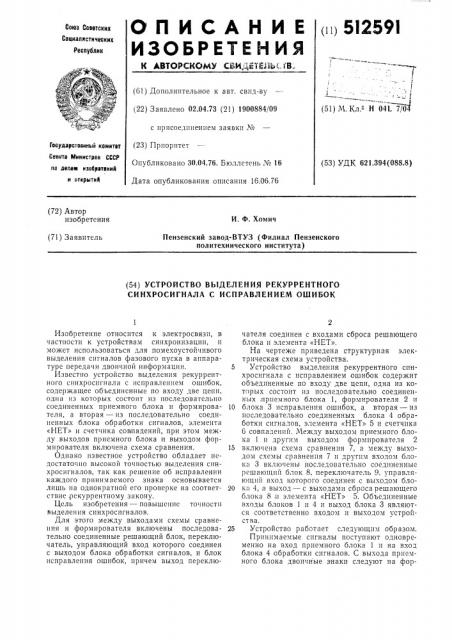

На чертеже приведена структурная электрическая схема устройства.

5 Устройство выделения рекуррентного спнхросигнала с исправлением ошибок содержит объединенные по входу две цепи, одна из которых состоит из последовательно соединенных,приемного блока 1, формирователя 2 и

10 блока 3 исправления ошибок, а вторая — из последовательно соединенных блока 4 обработки сигналов, элемента «НЕТ» 5 и счетчика

6 совпадений. Между выходом приемного блока 1 и другим выходом формирователя 2

15 включена схема сравнения 7, а между BblxOдом схемы сравнения 7 и другим входом блока 3 включены последовательно соединенные решающ)ьй блок 8, переключатель 9, управляющий вход которого соединен с выходом бло20 к", 4, а выход — с выходами сброса решающего блока 8 и элемента «НЕТ» 5. Объединенные входы блоков 1 и 4 и выход блока 3 являются соответственно входом и выходом устройства.

25 Устройство работает следующим образом.

Принимаемые сигналы поступают одновременно на вход приемного блока 1 и на вход блока 4 обработки сигналов. С выхода приемного блока двоичные знаки следуют на фор512591

Формула изобретения хаР

Составитель Г. Теплова

Техред А. Камышникова

Редактор T. Рыбалова

Корректор А. Степанова

Заказ 1216/10 Изд. № 1584 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2 мирователь 2 и схему сравнения 7, Результаты сравнения поступают на решающий блок

8, реализующий исправление ошибочных знаков в соответствии с системой и рекуррентных уравнений для каждого принимаемого знака последовательности, и представляющий собой >т-значный регистр сдвига.

Решающий блок 8 вместе с переключателем 9 реализует два алгоритма декодирования в зависимости то того, принят анализируемый знак рекуррентной последовательности в нулевой зоне или нет. Если анализируемый знак принят вне нулевой зоны (т. е. имеет определенную вероятность быть правильным), то исправление этого знака производится только при нарушении всех >г рекуррентных уравнений. Если знак принят в нулевой зоне (т. е. имеет определенную вероятность быть ошибочным), то его исправление производится и при наличии некоторых уравнений, удовлетворяющих коду.

Устройство выделения рекуррентного синхросигнала с поправлением ошибок, содержащее

5 объединенные по входу две цепи, одна из которых состоит из последовательно соединенных приемного блока и формирователя, а вторая — из последовательно соединенных блока обработки сигналов, элемента «НЕТ» и счет10 чика совпадений, при этом между выходом приемного блока и выходом формирователя включена схема сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения точности выделения синхросигналов, ме>жду выходами схемы

15 сравнения и формирователя включены последовательно соединенные решающий блок, переключатель, управляющий вход которого соединен с выходом блока обработки сигналов, и блок исправления ошибок, причем выход

20 переключателя соединен с входами сброса решающего блока и элемента «НЕТ».