Последовательный стабилизатор напряжения

Иллюстрации

Показать всеРеферат

ОП ИСА

Союз Советских

Социалистических

Республик

М Й4Зба

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМХ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заивлено29.11.74 (21} 2079730/24-7 (51) М. Кл. с присоединением заявки ¹ (23) Нриоритет

605F 1/56

Государственный камнтет

Совета Министров СССР аа делам нэааретений и открытий (53) УДК 621.316. .722.1 (OSS.S) (43) Опубликовано 05.05 76Бюллетень № 17 (45) Дата опубликования описания 28.05.76 (72) Авторы изобретения

Л. Г. Галактионов и В. П. Дицык (71) Заявитель (54) ПОСЛЕДОВАТЕЛЬНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ.

Изобретение относится к области питания радиоэлектронной аппаратуры, в частности к стабилизаторам постоянного напряжения с высококачественными выходными параметрами и может быть применено в контрольно-измерительной аппаратуре, в устройтрах преобразования информации и других в микроэЛектронном исполнении.

Известны последовательные стабилизаторы с защитой от перегрузок и от корот- 10 ких замыканий, содержашие стабилизирующий усилитель с ограничителем на входе, выходной резистивный делитель, цепочки из стабилитрона и резистора, подключенные между шинами питания, регулируюший тран- 15 зистор и диоды. для зашиты от перегрузок.

Недостатком известных стабилизаторов является то, что они не обеспечивают одно» временную защиту регулируюшего транзистора и стабилизируюшего усилителя от перегрузок по току и коротких замыканий.

Мелью изобретения является обеспечение одновременной зашиты регулируюшего тран,зистора и стабилизируюшего усилителя от итерегруэок по току и коротких замыканий, а5

2 а также быстрого восстановления выходноI го напряжения после устранения перегрузок и коротких замыканий.

Эта цель достигается тем, что в предлагаемый стабилизатор введен дополнительный транзистор, база которого подключена к эмиттеру регулирующего транзистора, эмиттер подключен к выходной. шине стабилыза тора, а коллектор — к шине питания усилителя.

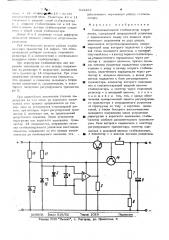

На чертеже представлена схема предло женного устройства.

Устройство содержит стабилизирующий операционный усилитель 1 с дифференциалт ным входом, регулируюший транзистор 2, ограничитель на диодах 3,4 для зашиты дифференциального входа усилителя, нагруэ ку 5 усилителя, эталонный резистор 6, делитель выходного напряжения на резисто рах 7,8, фильтруюшую емкость 9, две цепочки, состоящие из резисторов 10 11 и и стабилитронов 12,13 и дополнительного транзистора 14.

Йапряжение со стабилитрона l2 подает ся на шину питания стабилизнруюшего усили5133 >3

Тираж 1029

Подписное

>>>>ИИ>>И Звказ 818/52

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 а со сч йи»урбана 13 — на его

»>о»;: ;;>>т»рук щий вход. Резисторы I О и 1 1

> ос.дп и.»ы с входной i:,»íîé стабилизатора и с анодами стабилитронов 12 и 13 соо>-ветствоп»о, к >тоды стабилитронов соеди»е»ы с обиц Й и:иной стабилизатора. и ;оды 3 и 4 включены между дифференциала п»"4» входа:IH усилителя HGTpc÷íî-пара»лопь» о.

1!ри»омииа ц,»ом режиме работы стабилизатора транзистор 14 закрыт, что обес»ечивается выбором номинала этапонного резистора б в соответствии с номинальным выходным током стабилизатора.

При перегрузке стабилизатора или коротком замыкании на его выходе напряжение на резисторе 6 возрастает, вследствие чего транзистор 14 открывается. При этом напряжение питания усилителя снижается.

З-го приводит к снижению выходного напряжения усилителя и, следовательно, к некоторому запиранию регулирующего транзистора 2.

llpn даль»ейшем увеличении степени перегрузки (В TQM числе до короткого замыкания) этот процесс продолжается до тех пор, пока»е установится стационарный режим, при котором через регулирующий транзистор 2 протекает ток, не превышающий допустимого значения. После устранения перегрузки или. короткого замыкания транзистор 14 закрывается, напряжение питания стабилизирующего усилителя восстанавливается, напряжение »а его выходе увеличивается до номинального значения, что, обеспечивает»орлишьную работу стабилизатора.

Формула изобретения

Последовательный стабилизатор напряжения, содержащий операционный усилитель с подключенным между его входами ограничителем напряжения на двух диодах, включенных встречно-параллельно, инвер® тируюший вход которого подключен к средней точке выходного делителя, а неинвертирующий вход — к катоду первого стабилитрона „подключенного параллельно через резистор к входным клеммам, причем клемN мы питания усилителя подключены соотвеч ственно к аноду и катоду второго стабилитрона, включенного параллельно через резистор к входным клеммам, а выход усилителя подключен к базе регулирующего

39 транзистора, коллектор которого подсоединен к соответствующей входной клемме стабилизатора, а эмиттер через эталонный резистор — к выходной клемме, о т л ич а ю ш и и с я тем, что, с целью обеспечения одновременной защиты регулирующего транзистора и операционного усилителя от перегрузок.по току и коротких замыканий, а также быстрого восстановления выходного напряжения после устранения р перегрузки и короткого замыкания, стабилизатор снабжен дополнительным транзистором, база которого подключена к эмиттеру регулирующего транзистора, эмиттер подключен к выходной клемме стабилизатора, а коллектор - к клемме питания усилителя.