Ассоциативная ячейка памяти

Иллюстрации

Показать всеРеферат

СоюЗ Советских

Социалистических

Республик (11) 53.3393

М ! с

5 Р

»

4

»

1 (61) Дополнительное к авт. свнд-ву (22) Заявлено 09.08.73(21) 1956424/18 24 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.05.76Бюллетень № 17 (45) Дата опубликования опнсання12.05.76 (51) M Kn.

> 11 С 1WOO

Государственный комитет

Совета Министров СССР по делам нзооретеннй н PTKpblTNN (53) УДК 628.327 (088.8) (72) Авторы изобретения

Н.А, Зосимова и Я.И. Фет (71) Заявитель (54) АССОИИАТИВНАЯ ЯЧЕЙКА ПАМЯТИ

Изобретение относится к облети вычислительной техники.

Известна ассоциативная ячейка памяти, содержащая триггер и элементы управления записью-считыванием. Ь

Недостатками известной ячейки являются малое быстродействие, обусловленное необходимостью выполнения при ассоциативном поиске большого количества тактов, и большое число логических элементов и связей, »р что усложняет ячейку и матрицу ассоциативной памяти.

Белью изобретения является упрощение ассоциативной ячейки памяти и повышение ее быстродействия. »б

Поставленная цель достигается тем, что ассоциативная ячейка памяти содержит инвертор, логический элемент ИЛИ НЕ, парал» цельно соединенные вентили, ключевой и восстанавливающий вентили; .В йод инверторапод- и ключен к логическому входу ячейки, а выход иквертора - . к первому входу логическо» го элемента ИЛ -НЕ, второй вжд которого ,подключен к инверсному входу триггера, а

: выход - к управляющему входу ключевого . 35

2 вентиля, включенного между разрядной шиной единицы и шиной нулевого потенциала.

Передающие вентили включены между логи» ческим входом и логическим выходом ячейки, их управляющие входы подключены к пря мому выходу триггера и к разрядной шине единицы. Восстанавливающий вентиль включен между логическим выходом ячейки и шиной нулевого потенциала и подключен уа равляющнм входом к выходу инвертора.

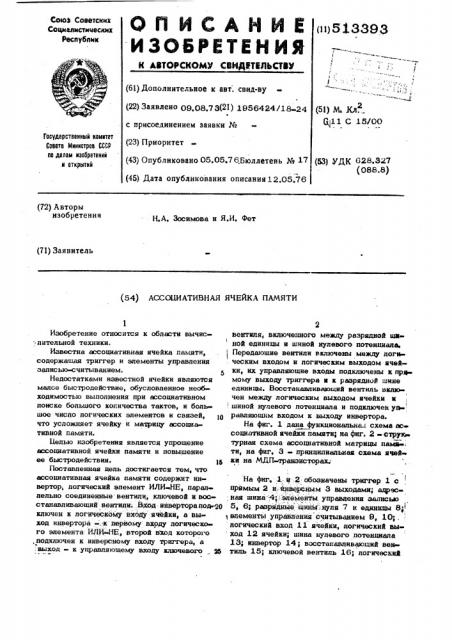

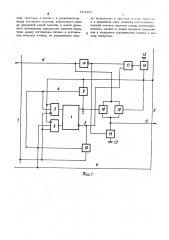

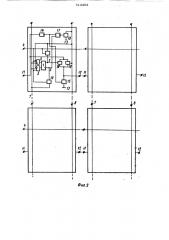

На фиг. 1 дана функциональнал схема ас» социатнвной ячейки памяти; на фиг. 2 - струк турная схема ассоциативной матрицы памя ти, на фиг, 3 - принципиальная схема ячвй» ки на МДП- гранзисторах.

На фиг 1. ii 2 обозначены триггер 1 с прямым 2 и:.йнверсным 3 выходами; адресная шина:4;:,;Элементы. управления записью

5, 6; разрядные шины нуля 7 и единицы 8; элементы управления считыванием 8, 10; .: логический вход 11 ячейки, логический выход 12 ячейки; шина нулевого потенциала

13; инвертор 14; восстанавливающий вен тиль 15; ключевой вентиль 16; логический

513393 элемент ИЛИ-HE 17 и параппепьно соединенные передаюшие вентили 18 и 19.

Ассоциативная ячейка памяти может работать в режимах хранения, записи, считывания и ассоциативного поиска информации, В режиме хранения адресная шина 4 на-. ходится на уровне логического "О, разрядные шины 7 и 8 - на уровне погической "1".

Обращение к ячейке для записи ипи считывания осуществляется подачей уровня 1

lO на адресную шину 4.

Элементы управления записью 5, 6 обес1 печивают установку триггера 1 в опредепенное состояние при наличии противоположных логических уровней на разрядных шинах 7, И

8 ячейки.

Элементы управления считыванием 9, 10, представпяюшие собой передающие вентили, обеспечивают передачу такового сигнала через находяшуюся на уровне логической "1 разрядную шину 7 ипи 8 на выход

2 или 3 триггера 1 выбранной ячейки, фиксируя на выходе этой шины логическое состояние ячейки, При "О" на входе 11 выход 12 ячей» ки оказывается на уровне шины нупевого потенциала 13 (погического "О"), так как входной сигнал, проходя через инвертор 14, открывает восстанавливающий передающий вентиль 15, включенный между логическим З> выходом ячейки и шиной нулевого потенциала 13, При объединении ассоциативных ячеек в однородную двухмерную ассоциативную мат рицу (см.фиг. 2), появляется возможность выделения при ассоциативном поиске максимального чиспа в течение одного такте обращения к ней.

В. режиме поиска максимального числа адресная шина 4 ячеек каждой строки матрицы находится на уровне логического "О, Элементы управления записью 5, 6 и считыванием Э, 10 каждой ячейки закрыты.

Разрядные шины 7, 8 ячеек каждого столбца матрицы подключаются к:уровню погической "1".

Потенциал разрядной шины 8 ячеек каждого столбца матрицы изменяется,еспи в одной и и нескольких ячейках столбца открыты ключевые передаюшие вентили 16, включенные между разрядной шиной 8 и шиной нулевого потенциала 13.

На вход 11 (и на вход инвертора 14) подается 1 в каждой ячейке левого столбца матрицы (старший разряд чисел). На один из входов погического элемента ИЛИ-НЕ

17 ячеек этого столбца поступает с выхо« па инвертора 14 О ° Если в ячейке хранится "О", то на второй вход элемента

ИЛИ-НЕ 17 подается 1" и на выходе эле4 мента ИЛИ-HE 17 устанаьпивается «О", запирающий кпючевой передающий вентиль

16.

При цапичии нулей во всех ячейках левого стопбца матрицы на разрядной шине единицы 8 остается потенциал 1, что приводит к отпиранию передающего вентиля 19 в каждой ячейке столбцов и прохождению

1 с входа 11 на выход 12 и далее на логический вход ячейки соседнего справа столбца матрицы. Еспи в некоторой ячейке левого столбца матрицы хранятся "1 то ключевой передающий вентиль 16 этой ячейки открыт и потенциал разрядной шины единицы 6 переключается на О, запирая передающий вентиль 19 каждой ячейки этого стопбца. Поданная на вход 11 каждой ячейки левого столбца 1" проходит на выход 12 только той ячейки, в которой передающий вентиль 18 открыт "1" на прямом выходе 2 триггера 1.

В результате "1 ", поданная на вход 1 1 ячейки, начиная с ячейки нового столбца (старшего разряда числа в каждой строке матрицы), прохо- . дит на выход 12 этой ячейки только в том случае, если в данной ячейке хранится "1" либо имеется сигнал о наличии нулей во всех ячейках соответствующего ей столбца. Логическая "1" на выходе 12 ячейки крайнего справа столбца (младшего разряда) по-! является топько в том случае, если в соответствуюшей этой ячейке строке находится максимальное число, Восстановление О" на выходе 12 в каждой ячейке происходит через открытый вос« станавливающий передающий вентиль 15 поспе подачи «Q на вход 11 каждой ячейки левого столбца матрицы.

Наиболее просто предлагаемая ассоциативная ячейка памяти может быть реализо-. вана на МДМ-транзисторах, где в качестве передающих вентилей может быть испопьзован один транзистор.

Формула изобретения

Ассоциативная ячейка памяти, содержа« шая триггер и элементы управления записьюсчитыванием, о т л и ч а ю ш а я с я тем, что, с целью упрощения ячейки и повышения ее быстродействия, она содержит инвертор, логический элемент ИЛИ НЕ, параппепьно соединенные передаюшие вентипи, ключевой и восстанавливающий вентили; причем вход инвертора подкпючен к логическому входу ячейки, а выход - к первому входу логического элемента ИЛИ-I-П- ., второй вход которого подкпюч - н K инверсному ebt513393

Фиг.f ходу триггера, а выход - к управпяюшему входу ключевого вентиля, включенного между разрядной шиной единицы и шиной нулевого потенциала;-передающие вентили включены между логическим входом и логическим выходом ячейки, их управляющие входы подключены к прямому пыхс>пу 1 игг< р» и к разрядной шине едпнинц восстанавпивающий вентиль включен между погичсским выходом ячейки и шиной нулевого потенциала и подключен управляющим входом к выходу инвертора

5 33О3

Фиг. 3

Составитель В. Гордонова

Техред О. Луговая Корректор C. Ьопдижар

Редактор Л. Утехина! илиад ПИ! Патент, r, Ужгород, уп. Гагарина 10.1

Заказ 4-07/21 Тираж 723 Подписное

ЦНИИПИ 1 осударсгвенного комитета Совета Министров СССР ло делам изобретений и открытий

1l3035, Москва, Ж-35, Раушская наб., д. 4/5