Импульсный усилитель

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (11) 813482

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-вф . 468363 (22) Заявлено12.08.74 (21) 2052005 126-21 (51) М. Кл.

Н 03 К 5/02 с присоединением заявки М— (23} Приоритет(43) Опублиновано05.05.76.Бюллетень %17 (45) Дата опубликования описания 29.05.76

Государствеииый комитет

Совета Мийистроа СССР по делам изооретений и открытий (53) УДК 621.375Я18 (088.8 ) (72) Автор изобретения

В. И. Жуков (71) Заявитель (54 ) ИМПУЛЬСНЫЙ УСИЛИТЕЛЬ

Изобретение относится к автоматике и, вычислительной технике и может использо:ваться в выходных каскадах логических ,схем.

Известен импульсный усилитель по основному авт.св. J4 468363, содержащий статический триггер с резистивными кол.— лекторно-базовыми связями и эмиттерный ,повторитель на двух последовательно соедйненных, транзисторах, Разброс параметров я транзисторов, а также использование мощных

:транзисторов с больщим временем закрывания сни.кают надежность известного импульсного усилителя.

С целью повышения надежности устрой- 15 ства в него введены две линии задержки, входы которых подключены к выходам статического григгера, а выходы — к его входам.

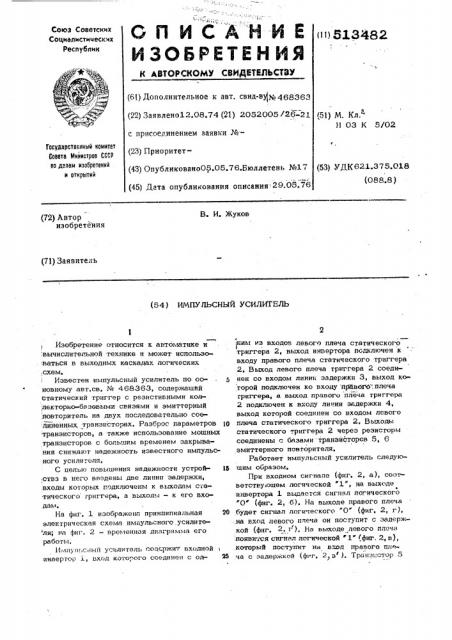

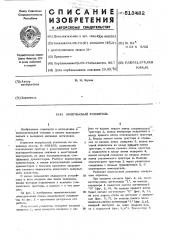

На фиг. 1 изображена принципиальная 20 электрическая схема импульсного, усилите ля; на фиг. 2 — временная диаграмма его работы, Имнул.,с алый у:илитель соцсржит входной инвертор 1, вход которого соединен с ос - 25

2 ним из входов левого плеча статического триггера 2, выход инвертора подключен к входу правого плеча статического триггера

2, Выход левого плеча триггера 2 соединен со входом линии задержки 3, выход которой подключен ко входу прав и о; плеча триггера, а выход правого плеча триггера

2 подключен к входу линии задержки 4, выход которой соединен со входом левого плеча статического триггера 2. Выходы статического триггера 2 через резисторы соединены с базами транзисторов 5, 6 эмнттерного повторителя, Работает импульсный усилитель следук щим образом.

При входном сигнале (фиг. 2, а), сост ветству ошем логической 1, на выходе инвертора 1 выдается сигнал логического

"0" (фиг. 2, б). На выходе правого плеча будет сигнал логического "0" (фиг, 2, г), на вход левого плеча он поступит с задержкой (фнг. 2, г). На выходе левого плеча появится сигнал лсгнческой 1" (фиг, 2, в), который поступи Г на Bòü0ï правого пле ча с задержкой (фиг. 2 в ). Транл:стор 5