Интергрирующий анаого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сока Советских

Социалистических

Республик (11). (51 3491 (61) Дополиительное к авт, свид-ву 132863 (22) ЗаЯвлено 12.07.74 (21) 2045294/26-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.05.76, Бюллетень № 17 (45) Дата опубликования описания,28,0576 (51) М. Кл.

НОЗ К 13/20

Государственный нометет

Совета 1йнннстров СССР па делам изобретений и открытии (53) УДК 681.325 (088.8) (72) Автор изобретения

В. Д. Циделко

Киевский ордена Ленина политехнический институт им, 50-летия Великой Октябрьской социалистической революции (71) Заявитель (54) ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к измерительной технике.

Известен линейный аналого-цифровой преобразователь (авт. св. Н 132863), содержащий ключ, выход которого через интегратор и детектор нуля подключен к блоку управления. Выходы последнего подключены к управляющему входу вентиля, через который генератор опорной частоты соединен со счетчиком, и к управляющему входу ключа.

Известное устройство является линейным преобразователем аналоговой величины в код н не позволяет получать функциональную з" внсимость кода от входной величины.

Предлагаемый интегрирующий преобразователь отличается тем, что, с целью расширения функциональных воэможностей, в него введены последовательно соединенные интеграторы, выходы которых подключены через первый сумматор ко входу блока памяти, управляющий вход последнего соединен с выходом нуль-органа, один вход которого подключен к выходу первого интегратора, другой - к выходу источника преобразуемого напряжения, выход блока памяти соединен с одним входом второго сумматора, второй вход котарогосоединен с источником опорного напряжения, подключенным ко входу первого интегратора, а выход второго сумматора подключен ко входу ключа опорного напряжения, управляющий вход второго сумматора через схему "И" соединен с выходами разрядов счетчика.

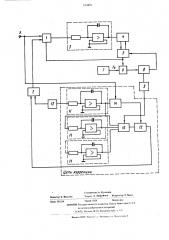

На чертеже представлена блок-схема интегрирую6 щего аналого- цифрового преобразователя.

На один из входов ключа 1 подается измеряемая .F ° величина л, к другому подсоединен сумм тор 2. Выход ключа соединен со входом интегратора 3, выход которого связан с детектором нуля 4, Детектор

10 4 соединен с блоком управления 5, выход которого подключен к схеме "И" 6 и ключу 1. Генератор опорной частоты 7 подключен ко второму входу схемы

"И" 6, выход которой соединен со счетчиком 8. Один выход счетчика подключен к блоку управления 5, 15 другой - к схеме "И" 9, выход которой соединен с сумматором 10. Входы сумматора подключены к выходам интеграторов 11, а его выход соединен с блоком памяти 12. Выход каждого интегратора соединен со входом последующего интегратора, а вход

20 первого из них подключен к источнику опорного на. пряжения 13. Второй выход источника опорного напряжения подключен к сумматору 2, второй вход которого соединен с выходом блока памяти 12, Выход первого интегратора 11 соединен с нуль-органом . 14, ко второму входу которого подключена вход Цепь КОррекции

Гоетавитель А. Кузнецов

Теарсд А. Аидрейчук Корректор 3. Фанта

Редактор Б. Федотов

Заказ 782 54

1ираж 1029 Подлисно

ЦНИИПИ Государственного комитета Говстз Министров (((Ð по делам изобретений н открьпий

113035, 51осквз, Ж-35, Рзушскзл нзб., д 4,5

Филиал ППП "Патента".1. Ужгород, ië 11роск нзи. 4