Устройство согласования ттл с мдп интегральными схемами

Иллюстрации

Показать всеРеферат

мах c..; йл) (:И А% б бил" : А

Союз Советских

Социалистических

Реса убяик (l1) 513602 (61) Дополнительиое к.авт. свид-ву (22) Заявлено1 9.07.74 (21) 2046931, /26-21 с мрнсоединением заявки № (23) Приоритет (Sl) М„Кл.

Н ОЭ К 19/00

Госудаустаааам, ааматат

Сааата Веастраа ИСР аа да}}аи ваабфжащЭ а аткраща (Я) 0публмковаио05,05.76.Бвллетемь №17 (M) УДК 621.374 (088.8) (46) Дата опубликования описания 28.05.76

Ю. М. Герасимов, А. Н. Кармазииский, В. М. Гусаков, Б. B. Орлов и С. l1. Штанько (72) Авторы изобретем ия (71) Заявитель (54) УСТРОЙСТВО СОГЛАСОВАНИЯ ТТЛ С МДП ИНТЕГРАЛЬНЫМИ

}СХЕМАМИ

Изобретение относится к электронике, электронной и вычислительной технике и предназначено для согласования низковольтных интегральных схем на биполярных транзисторах с высоковольтными интегралЬными схемами на дополняющих МДП-траизи<оторах.

Известно устройство согласования ТТЛ с МДП интегральными схемами, содержащее входной МДП-транзистор и инвертор на до .1(} полкяющых МДП-транзис-орах. Недостатками этого устройства являются значительная величина потребляемой мощности и ухудшение надежности.

С целью новыжения надежности и умень- 15 шеиия потребляемой мошиости в предложенное устройстВо введены два дополнительных инвертора иа дополняющих МДП-транзисторах; затвор- 1} -канального транзистора первого дополнительного кивер гора соединен 20 с выходом второго дополиительиого внвертора, а эатво:р $ -канального транзистора второго дополнительного иывертора — с выходом первого дополнительного иивертора, !

:затворы и -канальных транзисторов первого 25 и второго дополнительных инверторов соединены со входом и выходом инвертора соот» ветственно.

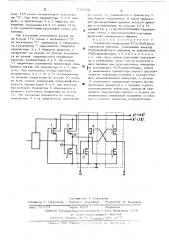

На чертеже представлена схема устройства, которое состоит из транзисторов 17 и источников напряжения 8, 9.

Транзистор 1 является нелинейным резистором и служит для повышения уровня

;логической 1 на выходе ТТЛ-схемы до

+5в. Транзисторы 2 и 3 образуют логичес кий инвертор, подключенный к источнику напряжения 8 (+5в). СхеMR преобразования уровней составлена иэ двух дополнительных сложных инверторов на транзисторах 4-7,,питаемых от источника напряжения 9(+10в).

13а"абверы $ -канальных транзисторов 4 и 6 ,первого и второго дополнительных сложных .ииверторов подключены к выходам 10 и 11 дополнительных сложных инверторов соовч ,вещественно, затворы g -канальных транэио»

epos 5 и 7 дополнительных сложных инверторов яодкаочены ко входу 12 и выходу

13 логического инверчора.

Схема работает следующим образом.

Пусть в исходном еостояння уровень на выЯ(1И)

Р(+И/!

Сосгянигг ль 1 . Богдяловя

Редактор 1 . Орловская Texpen !!. Лндрейчук Корректор Н. Ковалева

Закво 79 1/54 Тираж 102 9 Подписное

1111ИИГ!И Государствен> ого комитегя С ог»тя Министров СООР по л лял> иэо !>етений H < гк1>» гий

1 Л 30 >.>, No>cx>>a, >+ — »;, (;>ушс>>я», Hяб. >I.4 >>

Фи»t»!! 111!11 Пя > еи > ",;, . » or > >, v». lр "v > и >и, !

,ходе fTI1 схемы соответстьует логическому O При этом транзисторы 5 и F>;эякрыты, a транзисторы 4 и 7 открыты; потенпиалы на выходах 1 С> и 1 1 равны +1 0в и OB соответственно и состояние схемы устойчиво.

Прк изменении логического уровня ня на выходе ТТЛ схемы с логического О ня логическую "> транзистор 5 открывяе ся, втрянэистор 7 закрывается. Открытые транзисторы 4 и 5 образуют делитель, и напряжение ня выходе 10 быстро изменяется до уровня, определяемого отношением крутизны транзисторов 4 и 5, На выходе

11 напряжение изменяется значительно мед1 леннее, так как обв транзистора 6 и 7 закрыты. При правильном вь>боре крутизш.i транзисторов 4 и 5 (6 и 7 ) установившее- с. ÿ знячени» напряжения ня выходе 10 долж.— но быть меньш» напряжения отпирания)-кя-нми ных трянзи.торов 4 и 6, при досгчжении которого транзистор 6 открывается и начинает изменяться напряжение ня выход>

1 1. >то изменение передается нв затвор транзистора 4 и 0Н эякрь>вяется, напряжение ня выходе 10 уменья>ается и транзистор 6 еще больше G."êðûâaåòñÿ, Б схеме происходит ре> енервтивный процесс который приводи". к установлению на выходах 10 и 11 уровней Св и +10в соо;-ветственно. Переклюе кение схемы в противополо>иное состояние происходит аналогичным образом, Формула изобретени я

Ус.тройство согласования ТТЛ с МЧП кнтегральнь.ми схемами, содержащее входной ф

NOH-транзистор к инвертор на дополняющих

МЛП-транзисторах, о т л и ч я ю щ в eс я тем, что,c пель ю повышения наде жнос ти и уменьшения лотре" .яеN .oé мощности, в него введены двя до",îëíèòåëüíûõ инверторя

16

I на дополняющих NILLY-транзисторах, затвор

-канального транзистора первого дополнительного инверторя соединен с выходомвторого дополнительного кнвертора, а эятвор-квнального транзистора второго донолнигельного инверторя — с выходом первого дополнительного инвер-ора, затворы К -канальных транзисторов первого и второго дополнительных инверторов соединены со входом и выходом инверторя соответственно.