Логический элемент

Иллюстрации

Показать всеРеферат

Со.оз Советскик

Социалистических

Респу6лик о и и ;Х -ин и

ИЗОБРЕ? Е Н ИЯ (»)I5.19503

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сгид-ву(22) Заявлено02. 12. 74 (21) 2080480/26-2 1 с присоединением заявки № (23) Приорите (43) Опубликовано 05.05.765юллетень №17 (453 Дата опубликования описания 28.05.76

2 (51) M. Кл.

Н 03 К 19/08

Н 01 L 19/00

Государственный комитет

Совата Мнннотроа СССа ао долам нэоорвтоннй и открытий (53) бДК 681.325.65 (088.8) (72) Авторы изобретения

В. И, Лебедев и О. Б. Скворцов

Московский ордена Трудового Красного Знамени инженерно-физический институт (71) Заявитель (54) ЛОГИЧЕСКИИ ЭЛЕМЕНТ

Изобретение относится к полупроводнико вым логическим схемам, применяемым в ,цифровых вычислительных машинах.

Известен логический элемент, содержа,ший -p-и транзисторы, коллекторы кото- а рых подключены к инверсному выходу, а базы - ко входам элемента, р - и- р тран.зисторы, коллекторы которых соединены с

,базами соответствуюших и. — $- vlтранзис торов, эммнттеры - с положительной шиной Io

i источника питания, а баэ 1 подключены к объединенным эмиттерам и -p - и транзисторов, ч

Известный элемент недостаточно устойчив против помех отрицательной полярности, l5 а также не позволяет получать неинвертированную функцию входных переменных.

Цель изобретения — повышение помехоустойчивости и расширение функциональных возможностей — достигается тем, что в пред-20 лагаемый логический элемент введены дополнительные и -p- n. u p — и - р транзиоторы и источник тока; причем база дополниI тельного P — и- транзистора соединена с .объединенными базами -и-Р транзисторов, ба- И эа дополнительного и-р- 1 транзистора co- единена с инверсным выходом элемента и коллектором дополнительного 1 -и-р транзистора, коллектор дополнительного К- -И транзистора подсоединен к прямому выходу элемента, эмиттер - к объединенным эмнт терам vt -П вЂ” И транзисторов, а .эмпттер дополнительного p — и - транзистора подключен к положительной шине источника питания, причем эмиттерьп n -Jl — и, транзисторов

;подключены через источник тока к отрицательной шине источника литания. В качестве источника тока использован a - g — И транзистор, эмиттер которого соединен с отрицательной шиной источника питания, коллектор - с выходом источника тока, а база чв реэ транзистор в диодном включении с положительной шиной источника питания.

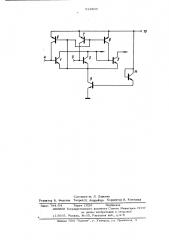

На чертеже показана схема логического элемента.

Эмнттеры и -p — и,транзисторов 1-3 сое динены вместе, базы транзисторов 1 и 2 подключены соотетственно ко входам 4 и

5 элемента, а коллекторы подсоединены к

„базе транзистора 3 и инверсному выходу

503

3 513 элемента. Змиттеры jl - ы-$ транзисторов )

6-8 подключены к положительной шине источника питания, а базы — к точ.е соединения эмиттеров транзисторов 1-3. Коллектор транзистора 6 подсоединен к баэетран-, эистора 1, коллектор транзистора 7 - к ба»

4 зе трачзистора 2, а коллектор транзистора

8 - к базе транзистора 3. Эмиттер и коллектор транзистора 9 и р — к типа присоединены соответственно к отрицательной шине источника питания и к точке соедине-, . © ния эмиттеров транзисторов 1 — 3, а 6аза соединена . через и -p- и транзистор

11 в диодном включении с положительной шиной 10 источника питания, причем эмиттер этого транзистора соединен с базой транзистора 9, а база и коллектор подсоединены к положительной шине.

Работает логический элемент следуюшим образом.

Пусть логической единице соответствует ® более положительное значение входного потенциала. Если на базах транзисторов 1 и

2 — низкий потенциал, соответствующий логическому нулю, транзисторы закрыты и весь коллекторный ток транзистора 8 попадает в базу транзистора 3, что обеспечивает его отпирание. В этом случае Н8 инверсном выходе логического элемента потенциал соответствует логической единице, а на прямом выходе, соединенном с коллекто ® ром транзистора 3 — логическому нулю, Если теперь ча один или оба входа логического элемента подать сигнал, соответствуюший логической единице и- - и транзистор, база которого соединена со входом, на кото- 44 рый подается логическая единица, открываеч ся, и потенциал точки соединения коллекторов транзисторов 1 и 2 падает до уровня, соответствующего логическому нулю. При этом коллекторный ток транзистора 8 почти полностью ответвляется в открывающийся транзистор, что вызывает запирание транзистора 3. Благодаря подключению эмиттеров транзисторов 1 — 3 к коллектору транзистора 9, образующего генератор тока, в 45

4ф логическом элементе наблюдается гисте зис, что позволяет получить выигрыш в помехоустойчивости для сигналов отрицательной полярности, а наличие прямого и инверсного выхода обеспечивает получение прямой и инверсной функции входных сигналов.

Формула изобретения

1. Логический элемент, содержащий

И -p — И транзисторы, коллекторы которых подключены к инверсному выходу, а базы — ко входа элемента, и f-u-р транзисторы, коллекторы которых соединены с базами соочветствуюших tl;P- и. транзисторов, эмиттерыс положительной шиной источника питания, а базы объединены и подключены к объеди» пенным эмиттерам h -р — и транзисторов, отличающийся тем, что,сцелью повышения помехоустойчивости и расширения функциональных возможностей:, в него ввелены дополнительные Ь- р — и. и P - - P транзисторы и источник тока, причем база дополнительного р- п-g,òpàíçèñòoðà соединена с объединенными базами — и-Р транзисторов, база дополнительного и-p-e транзистора соединена с инверсным выходом элемента и коллектором дополнительного — И-Р транзистора, коллектор дополнительного 1ър Ъ транзистора подсоединен к прямому выходу элемента, эмиттер — к объединенным эмиттерам

И -Я вЂ” и. транзисторов, а эмиттер дополнительного — к -P транзистора — к положительной шине источника питания, причем эмиттеры Q-p — и транзисторов подключены через источник тока к отрицательной шине источника питания, 2. Логический элемент по и. 1, о т— л и ч а ю шийся тем, что в качестве источника тока использован к -P — vt. транзистор, эмиттер которого соединен с отрицательной шиной источника питания, коллекторс выходом источника тока, а база через транзистор в диодном включении — с положительной шиной источника питания, 1

513503

Составитель Л. Дарьина

Редактор Б. Федотов Техред H. Андрейчук Корректор Н. Ковалева

Заказ 794/54 Тираж 1029 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и отхрь тий

113035, Москва, Ж 35, Раушская наб., д.4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4