Импульсно-потенциальный логический элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИНА

ИЗОБРЕТЕН ИЯ

1 ннитеитио-тох

Союз Советских

Социалистических

Республик (11) б 135О4

К АВТОРСКОМУ СВИДИВДЬСТВУ (б1) Дополнительное к авт. свид-ау (22) Заявлено15.02.74 {21) 1999362/26-21 с присоединением заявки № (23) Приоритет— (43) Опубликовано05.05.76,Бюллетень № 17 (45) Дата опубликования описания 20.05.76, (5)) M. Кл

H 03К 1. 9i14

ГееудвРстненнвй каетет

Вавета Мнннетрна СССР нн далем нзебретеннн н эткР4ВВгнй (53) УДК

621.382 (089.8) (72) Авторы изобретения

В. И. Осинский и К. Л. Тявловский

Институт электроники ЛН Белорусской ССР (71) Заявитель (54) ИМПУЛЬСНО-ПОТЕНПИАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ (Р4 Ма ... И„- т) т.

Изобретение относится к автоматике и вычислительной технике.

Известны логические элементы, содержащие входной многоэмиттерный транзис-, тор, коллектор которого соединен со входим сложного инвертора, выполненного на транзисторах .

Такие логические элементы являются потенциальными и не могут выполнять импульсн потенциальиых логических функ1 ций, что во многих случаях необходимо.

Пель изобретения — обеспечение им, пульсно-потенциального функционирования логического элемента, в частности вы полнение логической функции

Поставленная цель достигнута благодаря тому, что один или несколько эммиттеров входного многоэммиттерного тран,зистора подключены к общей шине через последовательно соединенные резистор и излучающий диод дополнительно введенного оптрона, фотоприемник которого включен

,между базой входного транзистора слож ного инвертора и обшей шиной.

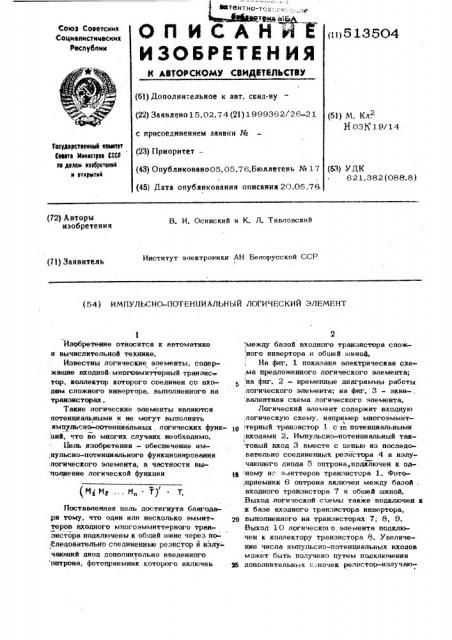

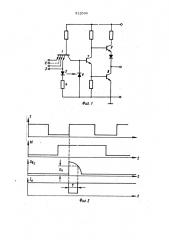

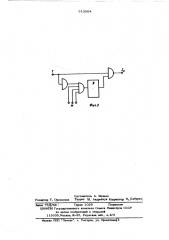

На фиг. 1 показана электрическая схе,ма предложенного логического элемента; на фиг. 2 — временные диаграммы работы

:логического элемента; на фиг. 3 — экви-. валентная схема логического элемента.

Логический элемент содержит входную логическую схему, например многоэммит1р терный транзистор 1 c,m потенциальными ,входами 2. Импульсно-потенциальный так товый вход 3 вместе с цепью из последовательно соединенных резистора 4 и marryчающего диода 5 оптрона,подключен к одуа ному из эмиттеров транзистора 1. Фотоприемник 6 оптрона включен между базой . входного транзистора 7 и обшей шиной.

Выход логической схемы также подключен к

:к базе входного транзистора инвертора, ре выполненного на транзисторах 7; 8, 9, Выход 10 логическог о элемента подключен к коллектору транзистора 8. Увеличение числа импульсно-потенциальных входов может быть получено путем подключения

25 дополнительных . .-.ïî÷åê резистор-излучаю51 3504 ций диод z эмиттерам транзистора 1, при этом фотоприемник 6 может быть общим для всех излучающих диодов.

При низком потенциале на тактовом входе 3 и высоком потенциале на всех ло гических входах 2 транзистор 1 насыщен а транзисторы 7 и 8 заперты. Транзистор

;9 открыт,. и на выходе 10 логического элемента поддерживается высокий уровень напряжения. Таким образом,при неизменяюаамся потенциале на тактовом входе ло-

i гический элемент выполняет функцию" -HE

При возрастании потенциала на тактовом входе 3 одновременно с ростом .напряжения на эммиттере транзистора 1 во растает и ток через излучающий диод 5.

Величина резистора 4 выбрана таким образом, что напряжение на тактовоЫ входе

3, соответствующее порогу срабатывания инвертора, вследствие возрастания фототока приемника 6 больше . или равно порогу срабатывания по логическим входам,, 1 . но меньше уровня логической 1 . При превышении входным напряжением порогового уровня логичэский элемент переходит во включенное состояние вследствие перехода транзистора 1 в инверсную активную область. Транзисторы 7 и B откроются, а транзистор 9 будет заперт. На выходе элемента будет действовать низкий уровень напрящения. Но через время, определяемое инерциашо тью оптрона 5 и фотоприемни» ка 6;, Фот» ток,"йриемника 6 возрастает до порогового значения и транзисторы 7 и 8 закроются.. На выходе 10 элемента будет действовать высокий уровень напряжения.

Твкнм образом, на положительный перепадмапряжения на тактовом входе 3 логический элемент вырабатывает отрицательный им; пульс напряжения, т. е. логический элемент,вы . цопняет импульсно-потенциальную функцик( цД ;где М-Сигнал на входах 2, Т-сигнал йа тактовом входе 3, d. - оператор перехода, соответствующий переключению Т из «1» в О . Например, запись dT означает положительный импульс, формируемый при переключении Т из 1 в 0". Этот уро" вень будет поддерживаться теперь током излучающего диода. Длительность формируемого импульса будет определяться в основ- ном инерционностью оптронной пары оптрон

5 - фотоприемник 6. Для надежного формиро- ванин импульса и запуска этим импульсом

Операция, выполняемая логическим эле

»Е ментом. может, быть записана в виде: j„-(M, М;... Мп Т) Т, где оперцня(М1 М, ...М Т) Т обозначает задержку функции(Ц Я ...Я на времяг,7 -длительность выходного импульса.

10 !

6 следующих логических элементов инерцион-! ность оцтронной пары должна в 1,5-2 раза

1 превышать инерционность основного логического элемента..

При уменьшении потенциала на тактовомвходе 3 напряжение на эмиттере трайзистора 1 уменьшится, быстрее, чем исчез нет фотопроводимость приемника 6. Транзистор 1 войдет в насыщение.и на базе транзистора 7 будет действовать низкий уровень напряжения независимо от излучения диода 5. На выходе элемента поддерживается высокий уровень напряжения, т.е. скема не реагирует на отрицательный перепад напряжения на тактовом входе .Б.лн

;же на axoilj будет опять подан положитель-:. ный перепад, то повторяются описанные

;процессы, и логический элемент формирует импульс.

Временные диаграммы, поясняющие работу элемента, приведены на фиг. 2. Здесь Т-сйгнал на тактовом входе элемейта, 1

М-сигнал на потенциальных входах элемена; 0Бд напряжение на базе транзистора 7, 1- выходной сигнал, Ц„- напряжение поро«„

ra. формула изобретения

Импульсно-потенциальный логический элемент, содержащий входной многоэми1 терный трчнзистор, коллектор которого соединен со BxolloM сложного инвертора, вы-. полненного на транзисторах, о т л и ч аю шийся тем, что с пелью в щолнения логической функцииф» М .. Mq Т, один. или несколько эмиттеров входного многоэмиттерного транзистора подключены к общей шине .через последовательно соединенные резистор и изпучаюший диод дополнительно введенного оптрона, фотоприемник которого включан между базой входного транзистора сложного инвертора и обшей шиной.

51 ЭБО4.

Составитель А. Шевьев

Редактор T. Орловская Техред tH. Андращук Корректор; H,фабурка

Заказ 710/58, Тираж 1029 Подиисное

0НИЙПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035,Москва, -35, Раушская наб., n.4/5

Филиал ППП Патент", r. Ужгород, ул, Проектная 4