Делитель частоты с любым целочисленным коэффициентом деления

Иллюстрации

Показать всеРеферат

БАТИ.!1О-Т аХКИ > . ГЕ." 7 49 я

Соеэ Соаетемик

Социалистичесаа

Уесвублин (») 513597

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДИТВЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 05.08.74 (21) 2049294/26-21 (51) М. Кл „Н- ОЗК23/00 с присоединением заявки №

Гоаударотвоииый комитат

Сооата Миииотроо СССР оо долам изобретеиий и открытий (23) Приоритет(43) Опубликовано05,05.76 Бюллетень №17 (53) УДК

621,374,4 (088,8) (45) Дата опубликования описания20.05.76 (72) Авторы иэобретения

А, Н, Калашников и Н, И, Устинов (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ

С ЛЮБЫМ ЦЕЛОЧИСЛЕННЫМ КОЭФФИИИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике, может найти применение в различных радиоэлектронных устройствах.

Известен делитель с любым целочисленным коэффициентом деления, содержаший две схемы совпадения, подключенные первыми входами ко входной шине, выход первой из которых соединен с одним из входов счетчика, подключенного к дешифратору, а выход второй - с вы.ходной шиной.

13ель изобретения - повышение быстродействия и надежности схемы.

В предлагаемый делитель введены запоминаюшие триггер и третья схема совпадения, первый вход которого подк,лючен ко входной шине, второй — к вы.ходу дешифратора и ко входу второй с.хемы совпадения, а выход — к другому входу счетчика и к нулевому входу запомина,юшего триггера, единичный вход которого соединен с выходом второй схемы совпадения, а выход-- со вторым входом первой схемы совпадения.

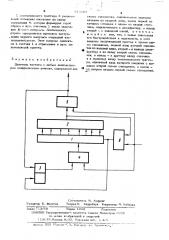

На чертеже представлена с.хема устройства, Делитель частоты с любым целочисленным коэффициентом деления состоит

5 из счетчика 1, дешифратора 2, запоминаюшего триггера 3 и схем совйадения

4-6.

Работает делитель следуюшим образом.

Входная последовательность импульсов через схему совпадения 6 поступает на счетчик 1 до установки в счетчике числа ф - 1 (при коэффициенте деления ф).

После окончания на входе делителя М- -to

;импульса с дешифратэра -2 поступает потенциал, который является запрешаюшим для схемы совпадения 6 и разрешаюшим для схемы совпадения 5. Импульс проходит через схему совпадения

5 на выходную шину и одновременно устанавливает в единицу триггер 3 ° который запоминает наличие выходйого сигнала до прихода первого импульса очедной последовательности.,"13:.>О7

Составитель М. Аудринг

Г едактор Б. Федотов Техред Н. Андрейчук Корректор H, Бабурна

3аказ 713/58, Тираж 1028 Подписное

11НИИПР(Государственного комитета Совета Министров (;(.:Ñ(-

no делам изобретений и откр итий

1 13(!35,Москва, Ж-35, Раущская наб., л, 4/5

Филиал ППП "Рант<- нт ", г.,Ужr ор эл, уп. 1 роектна и

C,;çàèoìèHîþùåãо триггера 3 разрешаинций потенциал поступает на схему совпадения 4, когорая формирует строб сброса в нуль счетчика 1 после окончания Я-ного импульса. Длительность строб определяется временем поступ,ления первого импульса очередной последовательности. Этот импульс заносится в счетчик 1 и сбрасывает в нуль запоминающий триггер.

r ч

Формула изобретения

Делитель частоты с любым целочисленным коаффициентом деления, содержащий две схемы совпадения, подключенные первыми входами ко входной шине, выход первой из которых соединен с одним из входов счетчика, подключенного к дешифратору, а выход второй - с выходной шиной, о т л и ч аю шийся тем, что, с целью повышения его быстродействия и надежности, в него введены запоминающий триггер и третья схема совпадения, первый вход которой подключен ко входной шине, второй - к выходу дешн-!

Ф фратора и ко входу второй схемы совпадения, а выход — к другому входу счетчика и к нулевому входу запоминающего триггера, единичный вход которого соединен с выходом второй схемы совпадения, а выход— со вторым входом первой схемы совпадения.