Цифровой делитель частоты с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Сеез Советских

Социалистических

Республик (11),5.3. 3 3<) & (61) Дополнительное к авт. свид-ву— (22) Заявлено 08. 08.7 4 (21) 205 097 2/ 26-2 1. (5j) M. Кл.

Я 03Jf 23/00 с присоединением заявки №

Гавудврвтввнхый кюивтвт

Свевтв Минввтрвв СССР ав двлвм хзвбрвтвний и вткрытий (23) Приоритет (43) Опубликовано 05.05.76,Бтоллетень № 17 (45) Дата опубликования описания 20.05.76 (72) Автор.. изобретения

Б. А. Пашков (71) Заявитель

L (54) ЦИФРОВОЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

С этой цепью в предпоженный депитепь частоты введены триггер„эпемент задержки, элемент запрета и формирователь выходного сигнала, Ко входам последнего подкпючены выходы триггере и зпемента ,задержки. Выход мпадшега разряда блока ! ,управления соединен с первыми, входами элементов запрета и задержки, на вторые входы которых поданы входные сигнапы, е к третьим входам подкпючен выход триггер а.

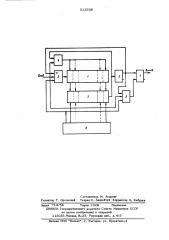

На чертеже представлена структурная схема цифрового депитепя астоты с переменным коэффициентом деления.

Делитель частоты содержит счетчик 1 с тт- разрядами, кодовь и компаратор 2 с формироватепем импульсов по дпнтепьности, элемент запрета 3 входных импупьсов, фсрмироватепь 4 входных импульсов, триггер 5, зпемент задержки 6., формирователь 7 выходного сигнала, блок управпения 8.

Делитель работает следующим образом.

Вхсдные счетные импупьсы проходят через нормально, открытый эпемент запре10

Изобретение относится к импульсной, технике и предназначено дпя испопьзования в качестве цифрового делителя частотыспедования импупьсов, имеющего переменный коэффициент делении, в устройствах, в KoTopblK желательно получение симметрич ной формы выходного напряжения типа меандр", например, в синтезаторах частоты, генераторах частотно-манипипупированных сигналов, Известен делитель частоты с переменным коэффициентом деления, содержащий счетчик, вход которого соединен со входом формирователя входных импульсов, а выходы - co входами кодового компаратора, к другим входам которого подкпючен блок управления.

В известном делителе установка кода производится один раз за период выходного сигнала, Это приводит к несимметричности формы выходного двухуровневого напряжения, Е1епью изобретения является попучение ,выходного сигнапа симметричной формы без снижения быстродействия. (53) УДЫ

681 374 43(088 8) 3 513

1та 3 н подсчитываютси счетчиком 1. В момент поразрядного совпадения кода счетчика 1 с кодом управления на выходе формирователя импульса кодового компарато ра 2 появляется импульс, который перебрасывает триггер 5, формируя первый полу периоц выходного сигнала, и одновременно запирает элемент запрета 3 и отпирает формирователь 4, При этом @чередной входной импульс йе проходит на счетный вход счетчика Я„а через формирователь

4 устанавливаеттрнггерыЬчетчика 1 в исходное состояние; сигнал на выходе кот дового компаратор 2 исчезает, и счетчик.

1 вновь начинает счет до появления следуюшего импульса установки.

В случае четного значения «ода управJ ленни коэффиииент деления получается четным, импульс установки появляется дважды за период выходного сигнала через равные промежутки времени, При нечетном коде управления элемент запрета 3 запрешает в первый полупериод, как и при четном коде, один входной импульс, а во второй полупериод в формирователе кодового компаратора 2 формируется импульс увеличенной длительности, который запрешает

Прохождение не одного, а двух входных ,импульсов, что приводит к увеличению длительности второго полунериода по сравнению с первым, на один период входного сигнала.

Для сохранения симметричности формы выходного сигнала при нечетных коэффициентах делении производится задержка заднего фронта первого полупериода на время, примерно равное половине периода входного сигнала.. Задержка фронта и запрет допол- кительного .входного импульса происходит при подаче отпираюшего потенииала от млад5Î8 шего разряд& xo$18 управления на эти схе» мы. Задержка фронта в элементе задержки

6 проиввшитеи е помоньи трвттерного фо .миров&тели на время, равною длительности входного импульс а.

В случае когда форма входного сигнала имеет вид меандра, выходной сигнал стр го симметричен, при отклонении формы входного сигнала от меандра отличие выход ного сигнала от симметричного невелико и

@ тем меньше, чем больше коэффипиент деле ния.

При входных частотщс, близких к пре;дельной в. качестве элемента задержки

|достаточно применения одного - двух логи® ческих инверторов. !

Формула изобретения Зи цифровой делитель частоты с переменным «оэффициентом деления, содержащий счетчик, вход которого соединен со входом формироватечя входных импульсов, а выходы - co входами кодового компаратора, к

ЗЭ другим входам которого подключен блок управления, отличающийся тем, что, с мелью получения выходного сигнала симметричной формы беэ снижения быстродействия, в него введены триг

N гер, элемент задержки, элемент запрета и формирователь выходного сигнала, ко входам последнего из которых подключены выходы триггера и элемента задержки, при этом выход младшего разряда

® .блока управления соединен с первыми входами элементов запрета и задержки, на вторые входы KOTopblK поданы входные сигналы, а к третьим входам подключен выход триггера.

513508

Составитель М, Аудринг

Редактор Т. Орловский Техред Н, Андрейчук Корректор Н. Бабурка

3аказ 714/58 Тираж 1029 Подписное

ЦНИИПИ Государственного;комитета Совета Министров СССР по делам изобретений и открытий

113035,Москва, Ж-35, Раушскан наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная,4