Мультиплексный канал с косвенной адресацией памяти

Иллюстрации

Показать всеРеферат

ОП ИОАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1111 5! 4287

СО1ОЗ СОВЕтсКИХ

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву (22) Заявлено 20.12.73 (21) 1980366, 24 с пр11сосдш1ением заявки . е (23) Приоритет

Опубликовано 15.05.76. Вюллстень М 18

Дата опуоликования описания 06.07.76 (51) Ч. К.."- G 06IF 3, 04 а O6F О1 О6

ГосуДарственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УД1| 681,325(088.8) (72) Авторы изобретения

К. К. Буряченко, А. Д. Доля и Е, Е. Редченкова (71) Заявитель (54) МУДЬТЙПЛЕКСНЬ1Й КАНАЛ

С КОСВЕт1 И ОЙ АДРЕСА ЦИ ЕЙ ПАМЯТИ

Изобретение относится к цифровым вычислительным системам.

Известен мультиплексный канал с косвенной адресацией памяти, содержагциЙ 0;IQK сопряжения с центральным процессором, первый вход которого подкзпочсн к первому входу каHB;IB, а псрВый ВыхОд соединен с первым Bblходом капала, блок сопряжения с центральной оперативной памятью, первый Вход которого подключен ко второму в|оду канала, а первые два выхода соединены соответственно со вторым и третьим вы|одами канала, блок сопряжения с внешними устройствами, первые вход и выход которого соединены соответственно с третьим, входом и четвертым выходом канала, блок основной памяти, блок адресной памяти, первый вы|од которого соединен с первым входом блока основной памяти, регистр подканала, два входа которого подключены соответственно ко второму выходу блока сопряжения с центральным процессором и второму выходу блока сопряжения с внешними устройствами, а выход соединен со вторыми входами блоков сопряжения с центральным процессором и внешними устройствами и с первым входом блока адресной памяти, регистр управления, дза входа которого подключены соответственно к выходу блока основной памяти и третьему выходу блока сопряжения с центральной оперативной памятью, регистр информации, три входа которого подкгпочены соответственно и вы|оду блока основной памяти, второму вы|оду блока сопряжения с внешпимп устройствами и третьему выходу

5 блока сопряження с центральной опсратиз. ой памятью, первы11 вы|од сосд1шеп со вторым

ЗХОДО. I 0;10i(B СОППЯЖ НИЯ С BHCHII:!11IH СТPOIIстзамп, а второй выход соединен со в .орымп

Входа ми Олока оснoBIIoll памят и и Ол01:.а со10 пряжения с центральной оператпзi Îl памятью, Олок модификации, Вход I(oTop0."О подключен к Вь1|оду регистра управления, а вы|од соединен с третьим входом блока сопряжения с центральной оперативной памятью и

15 вторым входом блока основной памяти, преобразователь кода адреса, выход которого соединен со вторым входом блока адресной памяти, первый регистр адреса. первый выход которого соединен со вторым и третьим входа20 ми блока адресной памяти и в|одом преобразователя кода адреса, а второй выход соединен с первым входом блока основной памяти, блок определения адреса, выход которого соединен со в|одом первого регистра адреса, а

25 первые дза в|ода подключены соответственно к первому и второму выходам блока адресной памяти.

Целью изобретения является повышение надежности работы мультпплексного канала. В

30 описываемом канале это достигается тем, что

514287 в нем дополнительно применены второй регистр адреса, генератор чисел и олок контроля ячеек зоны основной памяти мультиплекслого канала. Вход второго регистра адреса подключен ко второму выходу первого регистра адреса, а выход соединен с первым входом блока основной памяти. Два входа блока контроля подключены соответственно к выходам генератора чисел и блока основной памяти, а два выхода соединены соответственно с третьим входом блока определения адреса и вторым входом блока основной памяти.

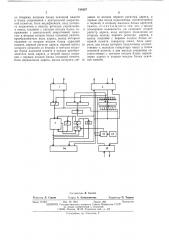

На чертеже приведена структурная схема описываемого мультиплексного кан ал а.

Схема содержит: 1 — блок сопряжения с центральным процессором; 2 — блок сопряжения с центральной оперативной памятью; 3— регистр подканала; 4 — регистр управления (регистр ключа защиты, регистр адреса команды (данных), регистр флажков, регистр кода операции, регистр счета данных); 5 — регистр информации; 6 — блок модификации адресов и счета данных; 7 — блок адресной памяти;

8 — преобразователь кода адреса; 9 — первый регистр адреса, фиксирующий адрес свободной (исправной) зоны основной памяти; 10— второй регистр адреса; 11 — блок определения адреса свободной зоны основной памяти;

12 — блок ко нтроля исправности ячеек зоны основной памяти; 13 — генератор чисел; 14— блок основной памяти мультиплеконого канала, предназначенный для хранения управляющей информации (программы) подканала (внешнего устройства); 15 — блок сопряжения с внешними устройствами.

Блок 7 предназначен для хранения таблицы адресов зон основной памяти мультиплексного канала и таблицы занятости (неисправности) этих зон. Таблица адресов зон основной памяти состоит из n, m-разрядных слов, где n— количество внешних устройств, подключенных к мульти плексному каналу; m — количество разрядов, достаточных для адресации всех зон основной памяти мультиплексного канала.

Объем таблицы занятости (неисправности) зон основной памяти (в,битах) равен количеству зон основной памяти. В таблице позиционно запоминается состояние зон основной памяти.

Инструкция состоит из 32 разрядов (Π— 31j (разряды 0 — 7 — инструкция, разряды 16—

18 — адрес канала, разряды 24 — 31 — адрес внешнего устройства). Адресное слово канала содержит 32 разряда (Π— 31j (разряды 0 — 3— ключ защиты, разряды 8 — 31 — адрес управляющего слова канала). Управляющее слово канала состоит из 64 разрядов (Π— 63) (разряды 0 — 7 — код операции, разряды 8 — 31— адрес данных, разряды 32 — 36 — флажки, разряды 48 — 63 — разряды счета данных).

В исходном состоянии адрес свободной (исправной) рабочей зоны блока основной памяти 14 хранится на первом регистре 9 адреса свободной зоны основной памяти мультиплексного канала. Определение исправности свооодной зоны основной памяти проводится сразу, после общего сброса канала, как это описано ниже.

При поступлении инструкции «Начать ввод — вывод» от процессора в канал блок 1 сопряжения с центральным процессором выдает потенциал инструкции и код номера внешнего устройства для фиксации на регистре подканала 3. Через блок 2 сопряжения с

1о центральной оперативной памятью производится прием в канал адресного слова канала и по нему — управляющего слова канала с фиксацией управляющей информации подканала на регистре управления 4. Модификация д адресов ячеек центральной оперативной памяти осуществляется блоком модификации 6, обмен данными с .внешними устройствами — через регистр информации 5. После пересылки кода операции внешнему устройству и окончания обмена между каналом и внешним устройством служебной информацией подканалу предоставляется свободная (исправная) рабочая зона блока основной памяти 14 для записи управляющей информации. Для этого со25 держимое первого регистра 9 переписывается на второй регистр 10 адреса основной памяти и используется в качестве адреса зоны основной памяти для хра нения управляющей информации данного подканала. Одновременно

Зз с записью управляющей информации в основной памяти производится фиксация номера предоставленной внешнему устройству ра бочей зоны в соответствующей ячейке таблицы адресов зон основной памяти мульЗб типлексного канала, а признака занятости этой зоны — в таблице занятости (неисправности) основной памяти мультиплексного канала. Таблицы хранятся в блоке адресной памяти 7. Фиксация этой информации в блоке памяти 7 производится за два цикла обращения к ней. Для этого номер внешнего устройства с регистра подканала 3 переписывается на регистр адреса адресной памяти, а содержимое регистра 9 —,на регистр слова адрес45 ной памяти. В первом цикле обращения к блоку памяти 7 происходит запись номера рабочей зоны основной памяти, выделенной в данный момент внешнему устройству, в ячейку таблицы адресов зон основной памяти, закрепленную за этим внешним устройством. После записи в таблицу адресов зон основной памяти содержимое младших разрядов регистра

9 переписывается через преобразователь кода адреса 8 на регистр слова блока памяти 7, а содержимое старших разрядов регистра 9— на место младших разрядов регистра адреса блока памяти 7, формируя адрес в таблице занятости (неиправности) зон основной памяти, Преобразование содержимого младших разgp рядов регистра 9 состоит в переводе параллельного двоичного кода в позиционный код адреса так, что каждой комбинации младших разрядов регистра 9 соответствует один разряд регистра слова адресной памяти. В стар65 шем разряде регистра адреса адресной памяти

514287

5 формируется признак обращения в таблицу занятости (неисправности) зон блока памяти

14 на регистр слова адресной памяти без предварительного сброса последнего, и в цикле восстановления информации производится запись признака занятости вместе со всеми уже имеющимися признаками.

Далее начинается поиск адреса новой свободной и исправной зоны основной памяти. В режиме поиска адреса свободной (исправной) зоны последовательно опрашиваются в блоке адресной памяти 7 все ячейки таблицы занятости (неисправности) зон блока памяти 14, а читаемая из адресной памяти информация анализируется в блоке 11 определения адреса свободной зоны основной памяти. При обнаружении «нуля» в прочитанном из адресной памяти слове содержимое регистра адреса адресной памяти переписывается в старшие разряды регистра 9 через блок 11,без преобразования, а содержимое регистра слова адресной памяти преобразуется блоком 11 в номер позиции «левого нуля» в слове, представленный после преобразования в параллельном коде и фиксируемый в младших разрядах регистра 9. Сформированный па регистре 9 адрес свободной зоны переписывается на регистр адреса блока освновной памяти 14, а генератор чисел 13 вырабатывает проверочную комбиницию, которая через блок контроля 12 исправности ячеек зоны основной памяти помещается на регистр слова блока основной памяти 14. Проверочная комбинация записывается в первую ячейку выбранной новой свободной зоны ос" овной памяти и читается из нее. Если комбинация прочитана верно (это определяет блок 12), записывается и прочитывается следующая комбинация, проверяется следующая ячейка зоны и т. д. После проверки всех ячеек зоны процесс отыскания свободной зоны завершается. Если результат проверки отрицательный, то в блоке памяти 7 в таблице занятости (неисправности) зон основной памяти для данной зоны фиксируется признак занятости (неисправности) и начинается процедура поиска адреса новой свободной зоны и ее проверки, как описано выше.

Для проверки исправности ячеек зоны основной памяти используются интервалы времени («паузы») между обращениями к основной памяти во время работы канала с внешними устройствами. При этом инструкция

«Начать ввод — вывод», приходящая от центрального процессора, не,начинает использоваться до окончания формирования адреса свободной и обязательно исправной зоны основной памяти, если такая ситуация возникает.

При появлении запроса абонента (внешнего устройства) на обслуживание номер внешнего устройства, полученный из интерфейса ввода — вывода через блок 15 сопряжения с в нешними устройствами, фиксируется на регистре подканала 3 и переписывается на ре30

65 гистр адреса адресной памяти с признаком обращения в таблицу адресов зон основной памяти. Из адрссной памяти :итается содержимое ячейки таблицы адресов зон основной памяти, закрепленных за выставившим запрос внешним устройством. Прочитанное слово используется в качестве адреса зоны, где хранится упр авл я ющая информация данного подканала. При возникновении ошибок в процессе чтения и записи управляющей информации из какой-либо зоны основной памяти корректируется таблица занятости (неисправности) зон основной памяти в блоке адресной памяти 7, и в дальнейшем эта зона основной памяти ло восстановления не используется.

Прог;;эмма работы этого внешнего устройства может быть повторена без остановки мультиплексиого канала для ремонта памяти.

После нормального завершения работы внешнего устройства (кроме случаев возникновения ошибок) в таблице занятости (неисправности) зон основной памяти, хранящейся в блоке адресной памяти 7, стирается признак занятости зоны и освободившаяся зона основной памяти пригодна для использования другим внешним устройством.

Формула изобретения

Мультинлексный канал с косвенной адресацией памяти, содержащий блок сопряжения с центральным процессором, первый вход которого подключен к первому входу канала, а первый выход соединен с первым, выходом канала, блок сопряжения с центральной оперативной памятью, первый вход которого подключен ко второму входу канала, а первые дза выхода соединены соответственно со вторым и третьим выходами канала, блок сопряжения с внешними устройствами, первые вход и выход которого соединены соответственно с третьим входом и чегвертым выходом канала, блок основной памяти, блок адресной памяти, первый выход которого соединен с первым входом блока основной памяти, регистр подканала, два входа которого подключены соответственно ко второму выходу блока сопряжения с центральным процессором и второму выходу блока сопряжения с внешними устройствами, а выход соединен со вторыми входами блоков сопряжения с центральным процессором и внешними устройствами H c первым входом .блока адресной памяти, регистр управления, два входа которого подключены соответственно к выходу блока основной памяти и третьему выходу блока сопряжения с центральной оперативной памятью, регистр информации, три входа которого подключены соответственно к выходу блока основной памяти, второму выходу блока сопряжения с внешними устройствами и третьему,выходу блока сопряжения с центральной оперативной памятью, первый выход соединен со вторым входом блока сопряжения с внешними устройствами, а второй выход соединен

И4287

Составитель И. Хазова

Техред А. Камышникова

Редактор Л. Струве

Корректор О. Тюрина

Заказ 1512/7 Изд. № 1343 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 со вторыми входами блока основной памяти и блока сопряжения с центральной оперативной памятью, блок модификации, вход которого подключен к выходу регистра управления, а выход соединен с третьим входом блока сопряжения с центральной оператив|ной памятью и вторым входом блока основной памяти, преобразователь кода адреса, выход которого соединен со вторым входом блока адресной памяти, первый регистр адреса, первый выход которого соединен со вторым и третьим входами блока адреоной памяти и входом преобразователя кода адреса, а второй выход соединен с первым входом блока основной памяти, блок определения адреса, выход которого соеди нен со входом первого регистра адреса, а первые два входа подключены соответственно к первому и второму выходам блока адресной памяти, отл и ч а ю щи и с я тем, что, с,целью

5 повышения надежности, он содержит второй регистр адреса, вход которого подключен ко второму выходу первого регистра адреса, а выход соединен с первым входом блока основной памяти, генератор чисел, блок конт10 роля, два входа которого подключены соогветствен но к .выходам генератора чисел и блока основной, памяти, а gaia выхода соединены соответственно с третьим входом блока определения адреса и вторым входом блока основ15 ной памяти.