Устройство для суммирования

Иллюстрации

Показать всеРеферат

1 1 5I4293

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со1оз Советских

Социалистических

Реслчблик гф

/ дф ф (61) Дополнительное к авт. свид-ву (22) Заявлено 27.05.74 (21) 2027695/24 (51) М. Кл б 06F 7/50 с присоединением заявки №. осударствеииый комитет

Совета Министров СССР оо делам изобретений и открытий (23) Приоритет

Опубликовано 15.05.76. Бюллетень № 18

Дата опубликования описания 06.07.76 (53) УДК 681.325(088.8) (72) Авторы изобретения

Б. А. Борковский, А. Ф. Катков и В. П. Романцов

Институт электродинамики AH Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ

Изобретение относится к вычислительной технике и может быть использовано как для вычисления алгебраической суммы по слагаемым, так и любого из слагаемых по заданной сумме и второму слагаемому.

Известно устройство для суммирозания, содержащее комбинационный и-разрядный сумматор, элементы «НЕ» и 2п» полусумматоров.

Однако известное устройство не .может быть использова но для,вычисления любого из слагаемых по заданной сумме и второму слагаемому.

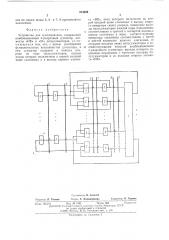

Целью изобретения является расширение фувкциональных возможностей сумматора. В описываемом устройстве это достигается тем, что в нем сумматор содержит в каждом разряде по IIaipe полусумматоров, первые входы которых подключены к.первой входной шине слагаемых и к выходу первого элемента

«НЕ»,,вход которого подключен ко второй входной шине слагаемых и выходу второго ин вертора своего разряда, инверсные выходы полусумматоров .каждой пары подключены соответственно к третьей и четвертой входным шинам слагаемых и через соответствующие инверторы соеди|нены соответственно с пятой и шестой входными шинами слагаемых, со вто|рыми входами своих полусумматоров и соответствующими входами комбинационного иразрядного сумматора, выходы которого соеди нены поразрядно с третьими входами полусумматоров и со входами второго элемента «НЕ».

На чертеже приведено описываемое уст5 ройство.

Оно содержит комбинационный и-разрядный сумматор 1, «2п» потусумматоров 2, «4п» элементов «НЕ» 3 и входнь е шины слагаемых

4 — 9.

Пример. Вычисление значения слагаемого Х по заданным значениям суммы S и второго слагаемого 1 . Для этого на шинах 4 и 8 задают значения разрядов соответственно суммы S и слагаемого У, а на шинах 5 и 6— соответственно те же значения в обратном коде S u Y. После переходного процесса на шинах 9 и 7 получают значение слагаемого

Х соответственно в прямом и ооратном коде.

20 Для правильной работы необходимо обеспечить, чтобы задержка по входам полусумматоров, соединенных с их выходами, равнялась

2Л задержке по остальным входам полусумматоров и по входам слагаемых комбинационного сумматора — равнялась 2 I, а по входам переноса сумматора из младшего разряда — 4Л.

Заметим, что шины 4 — 9 в за висимостп от операции могут использоваться как для вво30 да операидов, так и для вывода. Ввод операи514293

Формула изобретения

Составитель В. Соколов

Техред А. Камышникова

Редактор Л. Тюрина

Корректор О. Тюрина

3":;àç 1512/12 Изд. № 1343 Тираж 864 Подпи ос.

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035. Москва, М(-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 дов по парам шины 6, 8 и 7, 9 производится аналогично.

Устройство для суммирования, содержащее комбинационный и-разрядный сумматор, элементы «НЕ» и «2п» полусумматоро в, отлич а ю щ е е с я тем, что, с целью расширения

Функциональных возможностей сумматора, в нем сумматор содержит B каждом разряде по паре .полусумматоро в, первые входы которых подключены к первой входной шине слагаемых и к выходу первого элемента «НЕ», вход которого подключен ко второй входной шине слагаемых и выходу второго инвертора своего разряда, инверсные выходы полусумматоров каждой пары подключены

5 соответственно к третьей и четвертой входным шинам слагаемых и через соответствующие и нверторы соединены соот ветственно с пятой и шестой входными шинами слагаемых, со вторыми входами своих полугсумматоров и со10 ответствующими входами комбинационного и-разрядного сумматора, выходы которого соединены поразрядно с третьими входами полусуMMBTopo)B и со входами второго элемента «НЕ».