Устройство для управления регенерацией информации в динамической памяти

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 11) 5!4346

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТИЙЪСТВУ

Со?оэ Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 21.11.74 (21) 2077167, 24 с присоединением заягкп ¹ (23) Приоритет

Опубликовано 15.05.76. Eloëëåòå ?ь l, o 18

Дата опубликования o!II!c;;III!я 20.07.76 (51) М. Кл. G 11С 21/00

Государственный комитет

Совета Министров СССР

ll0 делам изобретений и открытий (53) УДК 681.327(088.8) (72) Авторы изобретения

Б. В. Барашенков и В. Е. Хавкин (71) Заявитель (54) УСТРОЙСТВО

ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ ИНФОРМАЦИИ

В ДИНАМИЧЕСКОЙ ПАМЯТИ

Изобретение относится к вычислительной технике и предназначено для использования в запоминающих устройствах (ЗУ) на ЧДПтранзисторах.

Известны устройства для управления регенерацией информации в динамической памяти, содержащие адресный блок, первые входы которого подключены ко входам устройства, вторые входы — к выходам шифратора, а выходы — к дешифратору, соединенному своими выходами с первыми входами элементов памяти, вторые входы которых подключены к блоку управления, а выходы — к элементу

«ИЛИ». В известных устройствах при поступлении требований на регенерацию от двух или более элементов памяти одновременно производится регенерация информации последовательным обходом всех адресов строк с помощью счетчика, что приводит к избыточному количеству тактов регенерацин.

Отличием описываемого устройства является то, что оно содержит элементы «И» и

«НЕ», причем выход каждого элемента памяти, кроме первого, соединен с первым входом соответствующего элемента «И» непосредственно, а со входами последующих элементов

«И» — через элементы «HF», выходы элементов «И» и первого элемента памяти, выход которого соединен со входами элементов «И» через элемент «HF», подключены ко входам шифратора. Зто позволяет повысить быстродействие устройства.

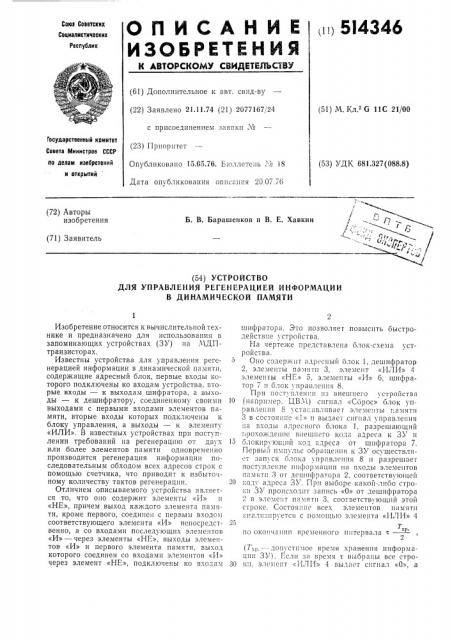

На чертеже представлена блок-схема устройства.

0Ho coQep>I! аЛресный олок 1, дешифратор

2, элементы памяти 3, элемент «ИЛИ» 4 элементы «НГ» 5, элементы «И» 6, шифратор 7!I блок уиравле?шя 8.

При по=туплен?.и из внешнего устройства

10 (например. ЦВ.Ч) сигнал «Сорос» блок управленllя 8 уста l:авлнвае Г элемеllты 1!2)IIITII

3 в состояш;е «1» и выдает сигнал управления

?а входы адресного блока 1, разрешающий

Г рохожде11ие B!lel!II!eго кода адреса к ЗУ и

15 блокиру?ощ??й коЛ адреса от шифратора 7.

Первы?1 импульс обращеш?я к ЗУ осуществляет запуск блока управления 8 и разрешает поступленile»»()op)!a!I!I!I на входы элементов памяти 3 от дешиф)a)opa 2, соответствуio!IIeII

20 коду адреса ЗУ, При выборе какой-либо строк» ЗУ происхолпт запись «О» от дешнфратора

2 в элемент Г?амяти 3. соответствующий этой строке. Состоя??1?е всех элементов памяти аi?2ëиэируется с помощью элемента «ИЛИ» 4 а

); т. по oKo!!÷àïèè в)еменного и??терва IB

XP °

2 (Т,-р — - допусти;loe время xpàíåíèÿ информа-!

IIII! ЗУ). Гслн за время т выбраны все стро30 к?i, элемент «ИЛИ» 4 выдает сигнал «О», а

514346 блок управления 8 разрешает прохождение внешнего адреса на в.;оды ЗУ через адресный блок 1. Если за время т, хотя бы одна строка не выбрана, элемент «ИЛИ» 4 выдает сигнал

«1», блок управления 8 запрещает прохождение внешнего адреса и разрешает прохождение адреса от шифратора 7 и через адреспый блок 1 на выход ЗУ, а также выдает во внешнее устройство сигнал «Занято», запрещающий обращение к ЗУ. Если сигнал «1» поступает от элемента памяти первой строки, то элемент «НЕ» 5, связанный с ним входом, образует на выходе сигнал «0», блокирующий выходы всех элементов «И» 6.

Таким образом, обеспечивается возбуждение только одного входа шифратора 7, связанного с элементом памяти 3 первой строки, и появление на выходе шифратора 7 кода адреса этой строки, проходящего через адресный блок 1 на вход ЗУ и дешифратора 2, При этом элемент памяти 3 первой строки переходит в состояние «0» и снимает через элемент

«НЕ» 5 блокировку элементов «И» 6, Аналогично сигнал «1» с выхода i-го из (т — 1) остальных элементов памяти 3 запрещает прохождение сигнала «1» с (т — i) элементов памяти через элементы «И» 6 с помощью соответствующего элемента «НЕ» 5, связанного со входами (m — i) элементов «И» 6.

Использование элементов «НЕ» 5 и элементов «И» 6, связанных как указано выше, обеспечивает однозначное возбуждение входов шифратора 7 и появление на его выходах адресов только тех строк, которые требуют регенерации, Если все элементы памяти 3 оказываются в состоянии «0» т. е. выбранными, элемент

«ИЛИ» 4 выдает сигнал «0», по которому блок управления 8 формирует сигнал, разре5 шающий доступ к памяти внешнего устройства, производится «сброс» схемы в исходное состояние, и работа схемы в следующем инт„, 2 протекает аналогично. тервале

Формула изобретения

15 Устройство для управления регенерацией информации в динамической памяти, содержащее адресный блок, первые входы которого подключены ко входам устройства, вторые входы — к выходам шифратора, а вы20 ходы — к дешифратору, соединенному своими выходами с первыми входами элементов памяти, вторые входы которых подключены к блоку управления, а выходы — к элементу «ИЛИ», отлич а ющееся тем, что, с

25 целью повышения быстродействия устройства, оно содержит элементы «И» и «НЕ», причем выход каждого элемента памяти, кроме первого, соединен с первым входом соответствующего элемента «И» непосредственно, а входа30 ми последующих элементов «И» — через элементы «НЕ», выходы элементов «И» и первого элемента памяти, выход которого соединен со входами элементов «И» через элемент «НЕ», подключены ко входам шифра35 торя.